主板硬件研发基础–HDMI工作原理

HDMI 接口

技术原理:HDMI 接口采用 TMDS 技术传输数字信号,不仅可以传输高清视频信号,还能同时传输多声道音频信号。它支持 EDID 和 DDC2B,设备之间能够自动协商并选择最合适的视频 / 音频格式,实现 “即插即用” 功能。接口类型:常见的有标准 HDMI 接口、Mini-HDMI 接口和 Micro-HDMI 接口。标准 HDMI 接口用于大多数电脑、电视等设备;Mini-HDMI 接口相对较小,常用于一些便携式设备,如相机、平板电脑等;Micro-HDMI 接口则更小,主要应用于智能手机等小型移动设备。性能特点:随着版本的更新,HDMI 接口的带宽不断提升,HDMI 2.1 接口标准带宽达到了 48Gbps,能够支持 8K 60Hz、4K 120Hz 视频以及 16bit 色深,还支持动态 HDR 数据传输、可变刷新率等功能。应用场景:广泛应用于机顶盒、DVD 播放机、个人电脑、游戏机、电视、数字音响等设备,是家庭影音娱乐系统中最常用的接口之一,也在广电节目制作、医疗手术直播、教育互动教学等领域有应用。

HDMI详细介绍

HDMI是新一代的多媒体接口标准。它能够同时传输视频和音频,简化了设备的接口和连线;同时提供了更高的数据传输带宽,可以传输无压缩的数字音频及高分辨率视频信号。

HDMI向下兼容DVI,但是DVI只能传输视频,而不能同时传输音频,这是两者最主要区别。此外DVI尺寸明显大于HDMI。

随着技术的迭代HDMI发展至今也推出了如干版本,性能更加出色,兼容性不断提高。HDMI正在成为高清时代普及率最高、用途最广泛的数字接口。

HDMI的优势

数字化视频、音频接口技术,是适合影像传输的专用型数字接口,其可同时传输视频和音频信号。

更好的抗干扰性能,能实现最长20米的无失真传输。

针对大尺寸数字平板电视分辨率进行优化,兼容性好。

完全兼容DVI接口标准

支持热插拔

一根线缆实现数字音频、视频信号同步传输,有效降低使用成本和繁杂程度。

HDMI电路原理

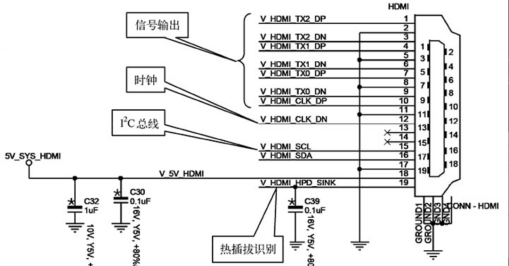

以下是对图中 HDMI 接口每根信号的详细介绍:

TMDS 数据传输相关信号

·V_HDMI_TX2_DP(针脚 2)、V_HDMI_TX2_DN(针脚 3):

·功能:构成 TMDS(Transition Minimized Differential Signaling,最小化传输差分信号)数据通道 2 的差分信号线。HDMI 通过 3 组 TMDS 数据通道来传输视频和音频数据,数据通道 2 主要负责传输一部分视频或音频信息。

·原理:差分信号传输方式利用两根线传输幅度相等、相位相反的信号,接收端通过检测两根线的电压差来还原数据,能够有效抵抗电磁干扰,保证信号在长距离传输过程中的稳定性和准确性。

·V_HDMI_TX1_DP(针脚 4)、V_HDMI_TX1_DN(针脚 5):

·功能:组成 TMDS 数据通道 1 的差分信号线,用于传输另一部分视频或音频数据,和其他数据通道协同工作,以完整传输一帧图像以及对应的音频数据。

·原理:同样基于差分信号传输原理,在高速数据传输中减少信号衰减和失真,确保数据准确无误地从发送端(如电脑显卡、蓝光播放器)传输到接收端(如电视、显示器)。

·V_HDMI_TX0_DP(针脚 6)、V_HDMI_TX0_DN(针脚 7):

·功能:构成 TMDS 数据通道 0 的差分信号线,负责传输视频和音频数据的一部分,三个数据通道共同协作,实现高清视频和多声道音频的高质量传输。

·原理:采用差分信号传输,提高信号的抗干扰能力,保证在复杂电磁环境下数据传输的可靠性。

·V_HDMI_CLK_DP(针脚 10)、V_HDMI_CLK_DN(针脚 11):

·功能:组成 TMDS 时钟通道的差分信号线,传输时钟信号。该时钟信号为数据通道提供同步参考,确保接收端能够按照正确的时序解析来自三个数据通道的数据。

·原理:通过差分信号传输时钟信号,保证时钟信号的稳定性和准确性,如同指挥家掌控乐队演奏的节奏一样,控制数据传输的节奏,使数据能够被准确接收和处理。

I²C 总线相关信号

·V_HDMI_SCL(针脚 14):

·功能:I²C 总线的串行时钟线(Serial Clock Line),为 I²C 总线上的数据传输提供时钟信号,协调数据传输的节奏。在传输 EDID(Extended Display Identification Data,扩展显示标识数据)等信息时,控制数据传输的时序,确保发送端和接收端之间数据传输的同步。

·原理:按照一定的频率产生时钟脉冲信号,数据在时钟脉冲的上升沿或下降沿被发送和接收,以此保证数据传输的准确性。

·V_HDMI_SDA(针脚 15):

·功能:I²C 总线的串行数据线(Serial Data Line),用于传输 EDID 等信息。EDID 包含了显示设备的型号、分辨率、刷新率、色彩模式等参数,信号源设备(如电脑、游戏机)通过读取这些信息,能够自动将输出信号调整为适合显示设备的最佳设置。

·原理:在 SCL 时钟信号的同步下,数据以串行方式在 SDA 线上逐位传输,实现设备之间的信息交互。

热插拔检测信号

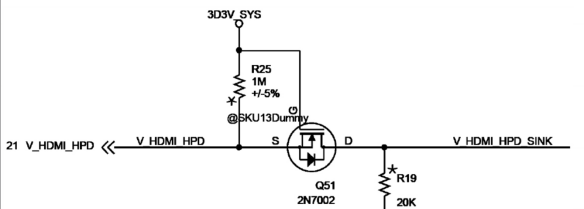

·V_HDMI_HPD_SINK(针脚 19):

·功能:用于热插拔检测(Hot Plug Detect,HPD)。当显示设备(如电视、显示器)通过 HDMI 接口连接到信号源设备(如电脑、蓝光播放器)时,该针脚会发送信号通知信号源设备显示设备已连接;当显示设备断开连接时,也会通过此针脚告知信号源设备,以便信号源设备进行相应的设置调整,如切换输出模式等。

·原理:当显示设备连接上时,HPD 信号线路会产生电平变化,信号源设备检测到这种变化后,会自动识别到新设备的接入,并进行相应的初始化和配置操作。

电源及其他信号

·5V_SYS_HDMI、5V_HDMI:

·功能:为 HDMI 接口及连接的设备提供电源,一般用于为接口电路中的芯片、元件等提供稳定的工作电压,确保其能够正常处理和传输数据。

·原理:通过电源线路将稳定的 5V 电压传输到接口电路中的各个元件,保证其正常工作。

·接地连接点(图中多处接地标识):

·功能:为整个接口电路提供电气参考电位,起到稳定电路、减少干扰的作用。接地良好可以降低信号噪声,保证信号传输的稳定性和设备的正常工作。

·原理:将接口电路中的各个元件的地线连接到一起,并与大地或设备的公共地相连,形成一个统一的零电位参考点,减少不同元件之间的电位差引起的干扰。

V_HDMI_TX_DP和V_HDMI_TX_DN是显示图像信号传输线,V_HDMI_CLK_DP和V_HDMI_CLK_DN是接口的时钟信号线,V_HDMI_SCL和V_HDMI_SDA是接口的I2C总线,V_HDMI_HPD_SINK是接口的热插拔识别信号。

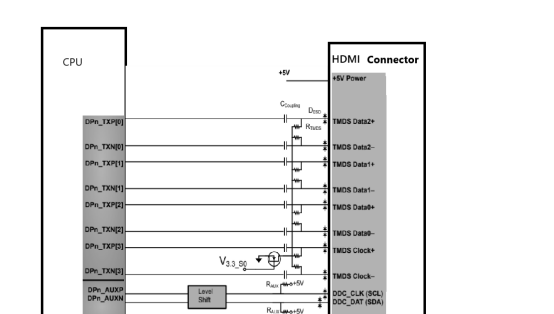

HDMI的结构框图

这是 HDMI(高清多媒体接口) 连接原理图,展示了 CPU(或 GPU,以下统称 CPU)与 HDMI 连接器之间的信号转换、传输及硬件设计逻辑。以下从 整体原理 和 关键设计细节 拆解:

一、整体原理:“信号转换 + 传输” 链路

HDMI 核心功能是 传输高分辨率视频、音频及控制信号(如热插拔、EDID 读取)。本图实现:

2.信号传输:通过 PCB 走线,将 HDMI 信号传递到连接器(公头 / 母头)。

3.功能覆盖:支持视频 / 音频传输、热插拔检测、EDID 读取(显示器参数协商)。

二、关键设计细节:逐模块 + 信号解析

1. 高速视频数据通道(TMDS)

HDMI 用 3 组 TMDS 差分对(Data0~2)传输视频 / 音频数据,1 组 TMDS 时钟差分对(Clock+/-)同步数据:

·功能:

·3 组数据差分对并行传输,支持高分辨率(如 4K)、高刷新率(如 60Hz)。

·时钟差分对为数据传输提供同步基准,避免误判。

·设计细节:

·阻抗匹配:TMDS 差分对需控制为 100Ω±10% 差分阻抗,保证信号完整性。

·滤波与隔离:图中串联电容(Ccouple)用于 隔直通交(阻断直流噪声,仅传输交流数据)。

·等长 / 等距:3 组数据差分对 + 1 组时钟差分对需严格等长(误差 < 50mil),避免相位差导致画面错位。

RTMDS相关电路的作用是给 4组 TMDS 差分信号提供直流分量,因为 4组 TMDS 差分信号在传输过程中经过了耦合电容,耦合电容会把直流分量过滤掉,因此在耦合电容后面需要一个提供直流分量的电路。

2. 辅助控制通道(DDC/CI)

·功能:

·传输 EDID(显示器参数):显示器通过 DDC_SDA/SCL 向 CPU 上报分辨率、色域、刷新率等参数,CPU 自动适配输出。

·支持 DDC/CI 指令(如显示器亮度调节、输入源切换)。

·信号组成:

·DDC_SCL(I²C 时钟) + DDC_SDA(I²C 数据):标准 I²C 总线,兼容低速控制需求。

·设计细节:

·上拉电阻(Rpull):V3.3_50 上拉到 3.3V,保证 I²C 总线空闲时为高电平(符合 I²C 协议)。

·电平转换:若 CPU 端电平与 HDMI 端不兼容(如图中 Level Shifter),需用电平转换芯片适配(如 1.8V→3.3V)。

3. 热插拔检测(HPD:Hot Plug Detect)

·功能:

·检测 HDMI 设备(显示器)是否插入 / 拔出,触发 CPU 重新协商信号(如识别新显示器、切换输出)。

·设计细节:

·电平转换:Level Shifter 适配 CPU 与 HDMI 端的电平(如 CPU 侧 1.8V → HDMI 侧 3.3V)。

·下拉 / 上拉逻辑:显示器插入时,HPD 引脚被上拉为高电平;拔出时回归低电平,CPU 通过电平变化判断状态。

4. 电源与接地(Power & GND)

·HDMI Power(+5V):

·为 HDMI 连接器供电(如驱动接口电路、EDID 存储芯片),电流较小(通常 < 50mA)。

·GND:

·多组 GND 引脚用于 信号回流(差分对的 “地参考”)和 屏蔽干扰。

·需保证 GND 平面完整(避免 “地分割”),降低噪声耦合。

5. 电平转换(Level Shifter)

·功能:

·适配 CPU 与 HDMI 设备的 电平差异(如 CPU 侧 1.8V/2.5V → HDMI 侧 3.3V)。

·常见于移动设备(如手机、平板),因 CPU 内核电压低,需转换后驱动外部接口。

·设计细节:

·需匹配 速率需求:辅助通道(DDC/HPD)是低速信号,可用简单电平转换芯片(如 TXB0108);高速视频通道通常无需转换(直接兼容差分电平)。

三、核心设计目标:“兼容性 + 信号完整性 + 可靠性”

1.兼容性:

·辅助通道(DDC/HPD)需严格遵循 HDMI 协议(CEA-861 标准),保证显示器被正确识别。

2.信号完整性:

·高速 TMDS 差分对需严控阻抗、等长、滤波,避免 反射、串扰、衰减 导致花屏 / 闪屏。

3.可靠性:

·电源滤波、接地设计需足够 robust,应对复杂电磁环境(如电脑内部 EMI)。

总结:HDMI 设计的 “3 大关键”

1.高速信号完整性(TMDS 差分对的阻抗、等长、滤波)。

2.低速控制兼容性(DDC、HPD 协议匹配 + 电平转换)。

3.电源与接地可靠性(滤波、平面设计,抗 EMI)。

理解这些,就能从原理图推导实际硬件的设计约束(如 PCB Layout 规则),也能快速定位 HDMI 接口 “不识别、花屏、闪断” 等问题~

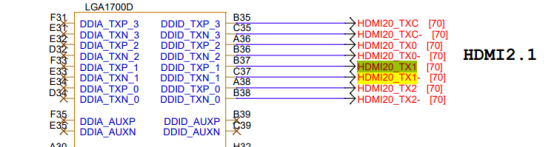

HDMI接口例子

当Sink准备好之后,HPD会给到Source,指示有Sink插入AUX(Auxiliary)传输设定与控制指令。包括读取扩展显示识别数据(EDID),以确保DP信号的正确传输;读取显示器所支持的DP接口的信息,如主要通道的数量和DP信号的传输速率;进行各种显示组态暂存器的设定;读取显示器状态暂存器。只有先保证AUX的信号正确才能使DP接口的信号正确传输。辅助通道(AUX Channel)作为DP接口中一条独立的双向传输辅助通道。

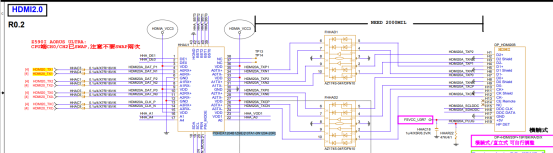

PI3HDX1204B1 是一款适用于 HDMI 2.0 6.0 Gbps 的 ReDriver™器件,核心功能围绕信号优化与转换展开,具体如下:

1. HDMI 2.0 信号增强与补偿

作为限幅型重驱动芯片,它能补偿高速 TMDS 信号在传输中的插入损耗,支持 6Gbps 速率下的信号传输。通过可编程的均衡(EQ)、输出摆幅(SW)和去加重(De-emphasis)控制,可优化不同物理介质(如线缆、电路板迹线)上的差分信号性能。其最大均衡值在 6Gbps 时可达 + 22dB,且附加抖动性能是传统 ReDriver 器件的 2 倍,能有效提升信号完整性。

2. 双模式 DisplayPort 电平转换

该芯片支持双模式 DisplayPort(DP++)到 HDMI 2.0 的电平转换应用,可将 DP 信号转换为符合 HDMI 2.0 标准的输出信号,实现不同显示接口间的兼容与信号适配。

3. 灵活的配置方式

其 EQ、输出摆幅和去加重参数可通过引脚绑定(pin-strapping)或 I²C 编程两种方式进行配置,能根据具体应用场景调整,以适配不同的传输介质和信号需求。

4. 辅助功能与特性

内置通道活动检测器,支持 50Ω 至 VCC 或 200kΩ 至 VCC 的可选输入端接;

具备独立的通道配置能力,可对每个通道的均衡、输出摆幅和去加重进行单独设置;

支持 3.3V 供电,工作温度范围覆盖 – 40℃至 85℃,适用于工业环境。

|

引脚号 |

引脚名称 |

类型 |

描述 |

|

数据信号 |

|||

|

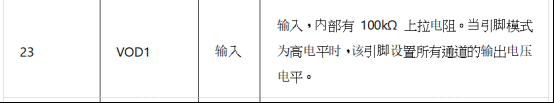

4、5 |

A0RX+、A0RX- |

输入 |

A0 通道的 TMDS 输入,内部有 50Ω 上拉电阻,否则为约 200kΩ 上拉电阻。 |

|

35、34 |

A0TX+、A0TX- |

输出 |

A0 通道的 TMDS 输出,内部有 50Ω 上拉电阻,否则为约 2kΩ 上拉电阻。 |

|

7、8 |

A1RX+、A1RX- |

输入 |

A1 通道的 TMDS 输入,内部有 50Ω 上拉电阻,否则为约 200kΩ 上拉电阻。 |

|

32、31 |

A1TX+、A1TX- |

输出 |

A1 通道的 TMDS 输出,内部有 50Ω 上拉电阻,否则为约 2kΩ 上拉电阻。 |

|

10、11 |

A2RX+、A2RX- |

输入 |

A2 通道的 TMDS 输入,内部有 50Ω 上拉电阻,否则为约 200kΩ 上拉电阻。 |

|

29、28 |

A2TX+、A2TX- |

输出 |

A2 通道的 TMDS 输出,内部有 50Ω 上拉电阻,否则为约 2kΩ 上拉电阻。 |

|

13、14 |

A3RX+、A3RX- |

输入 |

A3 通道的 TMDS 输入,内部有 50Ω 上拉电阻,否则为约 200kΩ 上拉电阻。 |

|

26、25 |

A3TX+、A3TX- |

输出 |

A3 通道的 TMDS 输出,内部有 50Ω 上拉电阻,否则为约 2kΩ 上拉电阻。 |

|

控制信号 |

|||

|

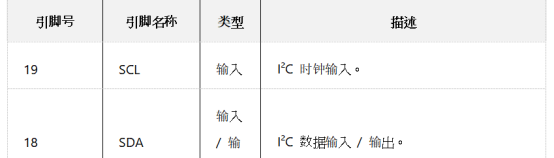

19 |

SCL |

输入 |

I²C 时钟输入。 |

|

18 |

SDA |

输入 / 输出 |

I²C 数据输入 / 输出。 |

|

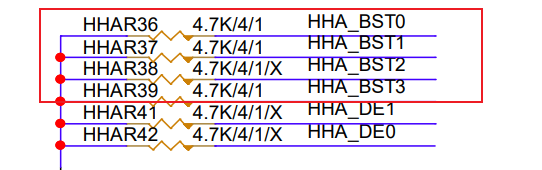

17、16、22 |

A4、A1、A0 |

输入 |

I²C 可编程地址位,内部有 100kΩ 上拉电阻。 |

|

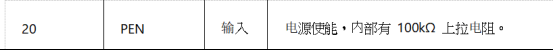

20 |

PEN |

输入 |

电源使能,内部有 100kΩ 上拉电阻。 |

|

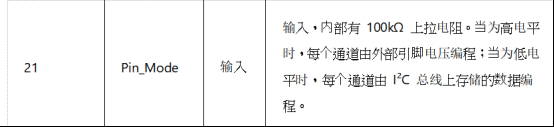

21 |

Pin_Mode |

输入 |

输入,内部有 100kΩ 上拉电阻。当为高电平时,每个通道由外部引脚电压编程;当为低电平时,每个通道由 I²C 总线上存储的数据编程。 |

|

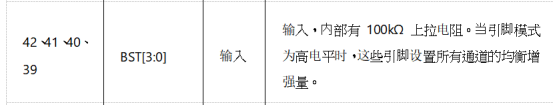

42、41、40、39 |

BST[3:0] |

输入 |

输入,内部有 100kΩ 上拉电阻。当引脚模式为高电平时,这些引脚设置所有通道的均衡增强量。 |

|

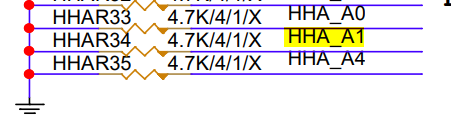

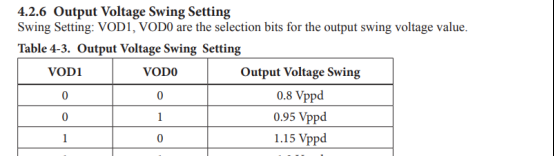

23 |

VOD1 |

输入 |

输入,内部有 100kΩ 上拉电阻。当引脚模式为高电平时,该引脚设置所有通道的输出电压电平。 |

|

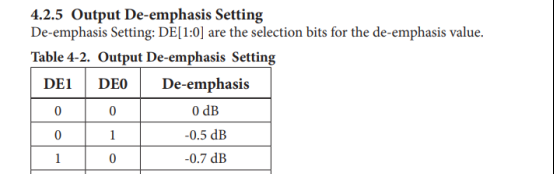

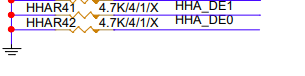

1、2 |

DE[1:0] |

输入 |

输入,内部有 100kΩ 上拉电阻。当 Pin_Mode 为高电平时,这些引脚设置所有通道的输出去加重电平。 |

|

38、37 |

NC |

未连接 |

未连接。 |

|

电源引脚 |

|||

|

6、12、30、中心焊盘 |

GND |

地 |

接地引脚。 |

|

3、9、15、24、27、33、36 |

VCC |

电源 |

电源供应引脚。 |

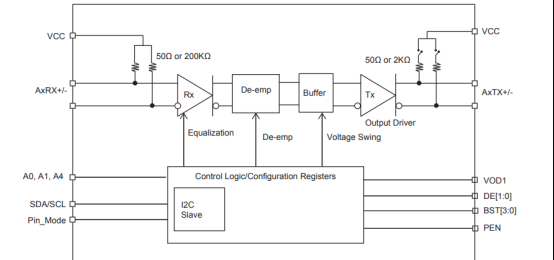

这是 PI3HDX1204B1 芯片的功能框图,可从信号流程和模块分工理解其工作逻辑:

一、信号流程(以单通道 AxRX±→AxTX± 为例)

输入接收(Rx):

来自外部的 TMDS 信号(如 HDMI/DisplayPort 数据)从AxRX±引脚输入,先经过50Ω 或 200kΩ 可选上拉电阻(适配不同输入场景),进入Rx(接收放大器)模块。

Rx 负责初步放大信号,同时通过 Equalization(均衡) 功能补偿信号传输中的高频损耗(比如线缆导致的衰减),让弱信号恢复 “清晰”。

去加重(De-emp):

信号进入De-emp模块,通过 De-emphasis(去加重) 进一步优化信号质量。原理是对信号高频成分做预补偿,抵消后续传输 / 输出可能产生的失真,确保信号完整性。

缓冲(Buffer):

经过处理的信号进入Buffer,主要起信号缓冲、驱动增强作用,为后级输出提供稳定的信号 “驱动力”,避免信号衰减影响输出质量。

输出驱动(Tx):

信号抵达Tx(输出驱动器),通过 Voltage Swing(电压摆幅) 功能调整输出信号的电压幅度,适配后级负载(如传输线缆、显示设备接口)。最后经 50Ω 或 2kΩ 可选上拉电阻 从AxTX±引脚输出,完成信号 “接收→处理→放大→输出” 的全流程。

二、控制与配置(Control Logic/Configuration Registers)

框图下方的Control Logic/Configuration Registers(控制逻辑 / 配置寄存器)是芯片的 “大脑”,功能分两部分:

I²C Slave:

支持 I²C 通信协议,可通过外部主控(如 MCU)的SDA/SCL引脚,对芯片内部寄存器进行编程。比如:

调整均衡强度、去加重等级、输出摆幅等参数;

配置芯片工作模式、地址(A0,A1,A4 用于设置 I²C 从机地址)。

引脚配置(Pin_Mode 等):

Pin_Mode:决定芯片配置方式。HIGH 时,通过外部引脚(VOD1/DE[1:0]/BST[3:0])的电平直接设置参数;LOW 时,优先使用 I²C 写入的寄存器配置。

VOD1/DE[1:0]/BST[3:0]:当Pin_Mode=HIGH时,这些引脚直接控制输出摆幅、去加重等级、均衡增强量,实现 “硬件直连式” 快速配置。

PEN:电源使能引脚,HIGH 激活芯片,LOW 关断以降低功耗。

三、核心价值:信号 “续命” 与灵活适配

简单说,PI3HDX1204B1 的功能可概括为 “信号修复 + 智能配置”:

对 HDMI/DisplayPort 等高速视频信号,通过均衡、去加重补偿损耗,让长距离传输后的弱信号恢复可用;

支持 I²C 和硬件引脚两种配置方式,适配不同应用场景(比如产线快速调试用引脚配置,系统级灵活控制用 I²C),确保信号质量的同时,给工程师留足设计自由度。

理解这张框图,就能抓住芯片的核心逻辑:通过模块化处理链修复信号,用控制模块实现灵活配置,最终保障高速视频数据稳定、高质量传输。

在 PI3HDX1204B1 芯片中,TMDS 信号从AxRX±引脚输入时设置 50Ω 或 200kΩ 可选上拉电阻,主要有以下几个作用:

1. 稳定输入电平

避免电平漂移:在没有外部信号输入时,引脚处于悬空状态,容易受到外界电磁干扰 ,导致引脚电平不稳定。上拉电阻可以将引脚电平拉高到一个确定的高电平状态(接近电源电压VCC ),从而保证输入信号在没有有效数据时处于稳定的状态,防止出现误判。例如,当外界干扰信号试图改变引脚电平,上拉电阻的存在使得引脚电平有一个恢复到高电平的趋势,提高了电路的抗干扰能力。

电平匹配:不同的设备或信号源输出的信号电平范围可能存在差异,通过选择合适的上拉电阻(50Ω 或 200kΩ ),可以将输入引脚的电平调整到芯片能够正确识别的范围内,确保芯片能够准确读取输入的 TMDS 信号。

2. 阻抗匹配

减少信号反射:TMDS 信号是高速差分信号,在传输过程中,如果传输线的阻抗与负载阻抗不匹配,就会产生信号反射,导致信号失真,影响信号的完整性 。50Ω 的上拉电阻可以起到一定的阻抗匹配作用,使得芯片输入引脚的阻抗与传输线的阻抗相匹配,减少信号反射。例如,在 HDMI 或 DisplayPort 的信号传输线缆中,其特性阻抗一般为 100Ω(差分阻抗),通过在芯片输入引脚设置合适的上拉电阻,能够更好地匹配传输线的阻抗,保证信号的稳定传输。

优化信号传输:对于不同长度或特性的传输线,可能需要不同的阻抗匹配策略。200kΩ 的上拉电阻可以在一些对信号传输要求不是特别高,或者传输线较短的场景下使用,在满足一定的信号完整性要求的同时,还可以降低功耗(相较于 50Ω 电阻,200kΩ 电阻的电流消耗更小)。

3. 降低功耗

灵活选择:根据实际应用场景选择不同阻值的上拉电阻,可以在保证信号质量的前提下,降低芯片的功耗。当信号传输距离较短,对信号完整性的影响相对较小,并且对功耗较为敏感时,可以选择 200kΩ 的上拉电阻,因为其阻值较大,流过的电流较小,从而降低了芯片的静态功耗 。而在信号传输距离较长,对信号完整性要求较高的场景下,则选择 50Ω 的上拉电阻,以确保信号的可靠传输。

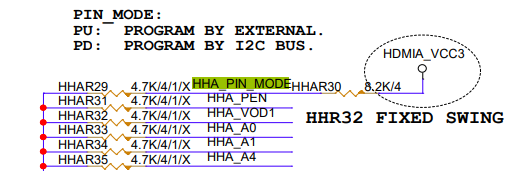

此电路PIN_MODE设置为高电平,所以是每个通道通过外部引脚电压设置去加重情况。

1、2 引脚(DE[1:0] )主要作用是在特定条件下设置所有通道的输出去加重电平,具体如下:

1. 电平设置与信号优化

当 Pin_Mode(引脚模式设置引脚)为高电平时,芯片采用引脚配置模式。此时,DE[1:0] 引脚通过内部 100kΩ 上拉电阻保持在一个相对稳定的电平状态, 并依据外部连接情况,即引脚所接的电平状态,来设置所有通道的输出去加重电平。

去加重是一种信号处理技术,主要针对高速数字信号。在信号传输过程中,高频分量会因传输线的损耗等因素而衰减得比低频分量更快,导致信号失真。通过去加重技术,在发送端对信号的高频分量进行增强,当信号到达接收端时,高频分量和低频分量的衰减程度能达到相对平衡,从而提升信号的完整性,减少码间干扰,使接收端能更准确地恢复原始信号。DE[1:0] 引脚提供了一种硬件配置方式,可快速、直接地调整去加重电平,以适配不同的传输介质和应用场景对信号质量的要求。

2. 灵活配置与应用场景适配

不同的传输场景,比如不同长度、材质的传输线缆,对去加重的需求不一样。较短的线缆可能只需要较小的去加重电平,而较长的线缆则需要更大程度地增强高频分量。DE[1:0] 引脚允许工程师根据实际的传输条件,通过改变引脚的连接状态(接地、接电源或者悬空等,具体取决于芯片手册中的配置表 ),轻松调整去加重电平,以达到最佳的信号传输效果。 相较于通过 I²C 编程的方式,引脚配置在一些对快速调试有需求的场景下,比如产品原型设计阶段,能更便捷地调整参数,提高开发效率。

表格是去加重的设置

在以下实际应用场景中,会设置去加重配置为 -1.0dB :

长距离高速信号传输场景

传输介质影响:当使用较长的传输线缆(如超过数米的 HDMI 或 DisplayPort 线缆 )来传输高速 TMDS 信号时,信号在传输过程中会经历显著的衰减,尤其是高频成分。线缆的阻抗、材质等因素都会导致高频信号损失严重。例如,在一些大型会议室或家庭影院系统中,从播放设备到显示设备之间的连接线缆可能长达 5 米甚至更长,此时高频信号的衰减会使信号质量下降,导致图像出现模糊、色彩失真等问题。

补偿需求:为了补偿这种高频信号的衰减,使接收端能够接收到完整、清晰的信号,就需要采用较大程度的去加重设置。-1.0dB 的去加重配置可以增强发送端信号的高频成分,当信号到达接收端时,高频和低频成分的衰减达到相对平衡,从而提高信号的完整性,保证显示设备能够正确显示图像和播放音频。

存在较多干扰的传输环境

干扰因素:在一些电磁环境复杂的场合,如靠近大型电机、变压器等设备的地方,信号传输会受到电磁干扰。这些干扰对高频信号的影响往往更大,可能会导致信号的高频成分发生畸变或丢失。例如,在工业控制环境中,各种电气设备产生的电磁干扰会严重影响高速信号的传输质量。

优化信号质量:通过设置去加重配置为 -1.0dB ,增强发送端信号的高频成分,能够在一定程度上提高信号的抗干扰能力。即使在传输过程中高频信号受到干扰而衰减,接收端仍有可能接收到足够强度的高频信号,从而准确恢复原始数据,确保设备的正常运行。

对信号质量要求极高的应用

应用需求:在一些对图像和音频质量要求极高的专业领域,如影视后期制作、高端游戏显示等场景,任何信号的失真都可能被察觉到。为了保证最终呈现的画面和声音效果完美无缺,需要对信号进行精细的处理。

去加重设置作用: -1.0dB 的去加重配置有助于最大程度地优化信号质量,减少高频信号衰减带来的影响,使显示设备能够呈现出更加清晰、细腻的图像,音频设备能够播放出更加逼真的声音,满足专业用户对高质量视听体验的需求。

这是 PI3HDX1204B1 芯片的均衡设置表,核心作用是通过 BST[3:0] 引脚组合,适配不同速率(6Gbps/8Gbps)信号的均衡补偿需求,直接影响高速信号传输质量。以下是关键分析:

一、核心逻辑:引脚编码→均衡补偿量

表格用 4 位二进制编码(BST3~BST0) 对应不同的均衡增益(dB 值),本质是给芯片 “设置处方”:信号传输衰减越严重(比如长线缆、高频损耗大),就选 更高 dB 值 的均衡,补偿信号丢失的高频成分。

|

编码规则 |

补偿目标 |

典型场景 |

|

BST [3:0] 全 0 |

最低均衡(0.25dB/0.4dB) |

短线缆、低损耗传输(比如板内) |

|

BST [3:0] 全 1 |

最高均衡(22.2dB/24.3dB) |

长线缆、高损耗场景(比如 HDMI 长距离布线) |

二、2 大 数据传输速率维度:6Gbps(3GHz) vs 8Gbps(4GHz)

表格区分了 6Gbps(对应 3GHz 频率) 和 8Gbps(对应 4GHz 频率) 两种场景,核心是 频率越高,信号衰减越严重,所以相同 BST 编码下,8Gbps 的均衡 dB 值更高。

比如 BST3~BST0 = 0000 时:

6Gbps(3GHz)仅需补偿 0.25dB,因为低频衰减小;

8Gbps(4GHz)需补偿 0.4dB,因为高频衰减更大。

再比如 BST3~BST0 = 1111 时:

6Gbps 补偿 22.2dB,8Gbps 补偿 24.3dB,高频场景对均衡需求更强烈。

三、设计意义:灵活适配 “信号损耗”

芯片支持这么多均衡档位,目的是 让工程师根据实际布线 / 场景动态调整:

量产调试:不同机型的线缆长度、材质不同,可通过 BST[3:0] 引脚硬件配置,找到最优均衡值,避免信号过补偿(导致失真)或欠补偿(信号模糊)。

复杂场景兼容:比如同一设备要同时支持短距离板内传输(低均衡)和长距离 HDMI 外接(高均衡),通过引脚配置即可灵活切换。

四、实操建议:怎么选?

先测损耗:用示波器抓接收端信号,看高频成分(比如信号上升沿、高频噪声)是否衰减。

从小到大试:从低均衡(BST 全 0)开始,逐步增加 dB 值,直到信号眼图(Eye Diagram)清晰、误码率降低。

优先看速率:如果是 8Gbps(4GHz)的高速场景,相同编码下补偿需求更高,直接对应表格右侧列。

简单说,这张表就是给工程师的 “信号补偿工具箱”—— 根据传输频率、线缆损耗选编码,让衰减的高速信号 “满血复活”,保障 HDMI/DisplayPort 等高带宽数据稳定传输。

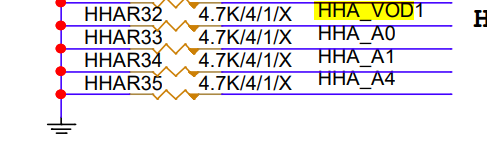

引脚:HHA_BST0、HHA_BST1、HHA_BST2、HHA_BST3

对应芯片功能:参考之前的均衡表,这 4 个引脚(BST[3:0] )组合起来,决定芯片对高速信号的均衡补偿量(补偿信号传输中的高频损耗 )。

当前配置:因为只有HHA_BST2没有通过 4.7KΩ 电阻下拉到地(4.7K/4/1/X 的/X表示不上件),所以BST3~BST0 = 0010,对应均衡表中补偿值(6Gbps 时 1.1dB、8Gbps 时 1.6dB )。

这样的配置主要基于以下几个方面的原因:

当 HDMI 线缆长度在 3~5 米时,6Gbps 信号(HDMI 2.0 版本的典型 lane 速率)的损耗刚好落在 0.8~1.2dB 区间,1.1dB 的均衡补偿能精准抵消损耗;若传输速率提升到 8Gbps(部分 HDMI 2.1 入门设备的 lane 速率),高频损耗会增加(速率越高,高频衰减越严重),此时 1.6dB 的补偿也能匹配对应损耗。

2. 中等质量的 HDMI 线缆:非屏蔽 / 细芯线缆(主流民用线缆)

HDMI 线缆的质量直接影响损耗,常见线缆类型的损耗差异如下:

高质量线缆:AWG 24~26 规格(线芯粗)、双层屏蔽(抗干扰),3 米长度下 6Gbps 损耗仅 0.6~0.8dB,无需此配置(用低补偿即可);

中等质量线缆:AWG 28~30 规格(线芯较细)、单层屏蔽或无屏蔽(如常见的 “高清线”“家用基础款线缆”),3 米长度下 6Gbps 损耗约 1.0~1.3dB,正好需要 1.1dB 补偿;

低质量线缆:AWG 32 以上(线芯极细)、无屏蔽,3 米损耗可能 > 1.5dB,需更高补偿(此配置不够)。

民用场景中,多数用户使用的是 “中等质量线缆”(价格 50~150 元,长度 3~5 米),此时BST3~BST0=0010的配置能完美适配这类线缆的损耗特性,避免因线缆质量不足导致的画面模糊、色彩失真、音频卡顿。

3. 特定 HDMI 版本与速率需求:HDMI 2.0/2.1 入门级设备

此配置对应的 6Gbps、8Gbps 速率,恰好匹配 HDMI 2.0 及 HDMI 2.1 入门设备的传输需求:

HDMI 2.0 设备:单 lane 最高速率 6Gbps,总带宽 18Gbps(支持 4K@60Hz),3~5 米中等线缆的损耗需 1.1dB 补偿,确保 4K 画质无拖影、无丢帧;

HDMI 2.1 入门设备:部分低端 4K@120Hz 设备(或简化版 HDMI 2.1),单 lane 速率可能降至 8Gbps(而非标准 HDMI 2.1 的 12Gbps),此时 1.6dB 补偿能抵消 8Gbps 信号的额外损耗,保证高刷新率画面的稳定性(如电竞显示器的 4K@100Hz 模式)。

三、电路设计视角:为何通过 “HHA_BST2 不上件” 实现此配置?

“只有 HHA_BST2 不上件(4.7K/4/1/X),其他 BST3~BST0 通过 4.7K 电阻下拉到地”,本质是主板厂商的 “预设适配主流场景” 设计 :

主流用户的 HDMI 使用场景(3~5 米中等线缆、HDMI 2.0/2.1 入门设备)恰好需要中等补偿(1.1~1.6dB),因此通过 “固定引脚配置”(不上件 HHA_BST2)将均衡值锁定在这个区间,避免用户因线缆 / 设备差异频繁调整;

若用户有特殊需求(如短距离高质量线缆,需低补偿;或长距离布线,需高补偿),可通过修改 BST 引脚的下拉电阻(如将 HHA_BSTx 改为上件 / 不上件)调整配置 —— 但这种 “预设中等补偿” 的设计,能覆盖 80% 以上的民用场景。

总结

当你的 HDMI 电路满足以下任一条件时,就需要BST3~BST0=0010(1.1dB/1.6dB 补偿)的配置:

使用3~5 米长度的 HDMI 线缆,且为常见的中等质量(非屏蔽 / 细芯)线缆;

连接的是HDMI 2.0 设备(如 4K@60Hz 电视 / 显示器)或HDMI 2.1 入门设备(如 4K@100Hz 电竞显示器);

信号传输环境无严重电磁干扰(仅靠近路由器、机顶盒等小型设备),信号损耗以 “线缆长度 / 质量导致的固有衰减” 为主。

若实际场景中出现画面闪屏、色彩偏差,可能是补偿值与实际损耗不匹配(如用了 5 米以上线缆却用此配置,补偿不足),需结合芯片手册的均衡表调整 BST 引脚的上件状态。

这些引脚(A4、A1、A0 )是芯片的 I²C 从机地址配置引脚,核心作用是 “让 1 颗主控(如 MCU)能区分多颗同型号芯片”,以下是详细拆解:

一、I²C 通信的基础逻辑

I²C 总线是 “一主多从” 架构(1 个主控 + N 个从机),所有从机共享 SCL(时钟)和 SDA(数据)线。为了让主控能精准 “点名” 某颗从机,每颗从机需要设置唯一地址。

二、A4、A1、A0 的作用:“地址编码”

这 3 个引脚通过电平高低(0 或 1)的组合,给芯片设置不同的 I²C 从机地址。

|

引脚电平组合(A4、A1、A0) |

对应的 I²C 从机地址 |

设计意义 |

|

000 |

基础地址 + 000(示例) |

同一总线上接多颗芯片时,用不同组合区分 |

|

001 |

基础地址 + 001(示例) |

避免地址冲突,让主控能单独控制某颗芯片 |

|

… |

… |

… |

三、内部 100kΩ 上拉的意义

引脚内部有 100kΩ 上拉电阻,默认电平为高(1):

若外部电路不做处理(悬空),引脚自动为高电平;

若需要设置为低电平(0),只需外接导线到 GND 即可。

这种设计让工程师不用额外加电阻,就能灵活配置地址(省成本、简化布线)。

四、实操场景:多芯片级联

比如在复杂显示系统中,可能用 2 颗 PI3HDX1204B1 扩展信号:

芯片 1:A4=0、A1=0、A0=0 → 地址 0xXX

芯片 2:A4=0、A1=0、A0=1 → 地址 0xXY

主控通过 I²C 发指令时,带不同地址前缀,就能单独控制某颗芯片的均衡、去加重等参数。

简单说,A4、A1、A0 是给芯片 “设身份 ID” 的引脚,通过电平组合让 I²C 主控能区分多颗同型号芯片,实现精准控制。

此电路设置为111

1. 引脚作用

在 PI3HDX1204B1 芯片里,VOD1、VOD0 引脚是用于设置输出电压摆幅(Output Voltage Swing)的选择位 。通过给这两个引脚设置不同的电平组合(0 或 1 ),能调整芯片输出信号的电压摆幅大小,以此适配不同传输场景对信号强度、驱动能力的需求,优化高速信号(像 HDMI/DisplayPort 信号 )传输时的信号完整性,补偿传输线路带来的损耗等。

2. 不同组合对应效果

结合表格看:

当 VOD1 = 0 且 VOD0 = 0 时,输出电压摆幅为 0.8 Vppd(峰 – 峰值差分电压 ),这种小摆幅适合对功耗敏感、传输距离短、负载轻的场景,能降低功耗,不过驱动能力相对弱些。

当 VOD1 = 0 、VOD0 = 1 ,摆幅是 0.95 Vppd ,摆幅有所提升,可适配稍长距离或稍重负载,在功耗和驱动能力间找平衡。

VOD1 = 1 、VOD0 = 0 时,摆幅达 1.15 Vppd ,适合传输距离较长、信号衰减多,需要更强驱动能力来保障信号质量的情况。

VOD1 = 1 、VOD0 = 1 时,摆幅 1.3 Vppd 最大,用于长距离、高损耗传输,或要驱动高负载(比如连接长线缆、多个接收设备 )的场景,用更高摆幅补偿信号衰减,让接收端能清晰识别信号 。

原理图里只有 VOD1 引脚,没 VOD0,可能原因:

芯片设计简化:芯片内部把 VOD0 功能固化(比如默认固定电平),只用 VOD1 实现基础摆幅调节,砍去 VOD0 简化硬件。

应用场景适配:实际电路(像短距传输)只需两种摆幅,VOD1 高低电平选就行,不用 VOD0 精细调,省元件、布线。

原理图省略:VOD0 内部已固定(接电阻 / 默认电平),原理图只画用到的 VOD1,简化绘图。

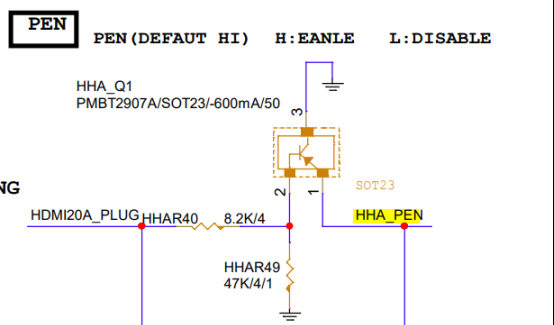

PEN 引脚是 电源使能控制引脚,核心作用是 “开关芯片的电源模式”,直接决定芯片是否工作,以下是关键解读:

一、基础功能:控制芯片上电 / 掉电

高电平(默认):内部 100kΩ 上拉电阻会把引脚拉到高电平(接近 VCC ),此时芯片正常工作,输入输出、配置功能全部启用。

低电平(外部拉低):若通过电路(如接 GND )将 PEN 拉低,芯片进入掉电模式(Power Down Mode),输入输出端接会被重置(比如输入 200K、输出 2K 欧姆),芯片停止信号处理,大幅降低功耗。

二、实用场景:灵活控功耗

待机 / 休眠:设备进入待机时,拉低 PEN 让芯片休眠,省功耗(比如显示器待机时,关闭 HDMI 信号处理)。

热插拔保护:外接设备(如显示器)插入瞬间,先拉低 PEN 避免浪涌冲击,稳定后再拉高启用芯片。

三、内部上拉的意义

内部 100kΩ 上拉电阻,默认保证芯片 “上电即工作”:

若外部电路不处理 PEN(悬空),引脚自动为高电平,芯片直接进入工作状态,简化设计(不用额外接电阻)。

如需掉电模式,只需外接一个开关或 MCU 引脚,轻松拉低 PEN 。

简单说,PEN 是芯片的 “电源总开关” 引脚,通过高低电平控制芯片工作 / 休眠,兼顾 “默认自动工作” 和 “灵活控功耗”,让设备在需要时省电、保护芯片。

三极管的基极接的是热插拔信号,当HDMI设备插上时,三极管不导通,HHA_PEN通过芯片内部的上拉电阻上拉为高电平,此时芯片正常工作;当HDMI设备拔出时,三极管导通,HHA_PEN被拉低,此时芯片进入掉电模式。

在芯片应用中,通过SCL和SDA引脚,主控设备能够与芯片进行通信,实现对芯片的各种功能配置(如设置芯片的工作模式、调整信号处理参数等)以及读取芯片的状态信息,使得芯片能够按照系统的要求正常工作。

主板硬件研发知识还是很难的,如果觉得文章哪里讲的不清楚,或者有哪些好的改进意见,欢迎提出和讨论~

相关文章