台积电OIP生态论坛把半导体I/O生态推到了一个新阶段。这不是一句空话——现场的技术路线、库的划分和验证难度,已经改变了设计和量产的玩法。

现场扎堆讨论的是,一套通用的“基础I/O库”已经满足不了目前的市场了。目前的现实是:一个工艺节点下,不再只有一两种I/O选项,而是要按应用分出好几条路线。高速计算、车载、移动和物联网,各自对速度、漏电、ESD、接口协议有不同要求。对于工程师来说,选库这件事变成了必须认真做的系统工程。说白了,随意用代工给的默认库,风险很大。

到这里先说点具体的变化。原先简单的GPIO,主要就是推挽LVCMOS或开漏,顶多加几个I2C、SMBus接口。放到目前,16nm/22nm节点下,一颗芯片常常要支持SPI、I3C、CAN、JTAG、RGMII、eMMC等多种协议,甚至在一样封装里服务于汽车和手机市场。为应对这些需求,出现了混合型的多协议I/O单元,像GPODIO这样的设计,可以在CMOS和开漏模式间切换,兼容多种标准,这类单元成了目前I/O设计的基础模块之一。挺有意思,接口不再是单一工具,而更像多功能刀。

再往细处看,有所谓的“超级I/O”宏单元。它可以包含两条单端或一对差分信号线,支持二十多种标准:LVDS、MIPI,还有带片上终端的HSTL/SSTL,以及POD等。这类宏单元更多出目前高性能计算和5G基础设施里,专门处理高带宽、低延迟的场景。还有人把射频和模拟I/O也拉进来:现成的低电容RF焊盘、匹配好的LVDS/HDMI对、甚至能承受高达20V的模拟I/O单元,都开始出目前标准库里,这减少了手工定制的工作量,也降低了设计风险。

库的多样化超级明显。以22nm为例,同一个GPIO设计可能演变成五个不同版本:面向超低功耗物联网的PM22(漏电流能降到0.14nA左右)、面向手机的平衡型MM22、车规级别的OG22(ESD抗扰度达8kV HBM)、以及面向高性能的EG22/TG22,后两者在封装和金属层上做了优化以提高密度。每个库在速度、漏电、ESD等级(从2kV到16kV HBM不等,CDM在6A到16A区间)、以及支持的接口上都有不同侧重。产品架构师目前得根据目标市场精细挑库,错配会影响性能或功耗。

封装演进也推着I/O变化往前走。2.5D/3D封装和芯片组间高速接口,带来了更高密度和更低功耗的片间I/O。举个现场提到的例子:在16nm工艺下,芯片间可以做到4Gbps级别的传输,同时保持极低的直流损耗,这是以前传统封装难以做到的。这样的进展让模块化设计、异构集成成为现实,但也带来了新的验证和信号完整性挑战。

验证复杂度这块,变化尤其大。过去那种GPIO验证大致需要135个PVT角点就能过关。现代I/O面对的是多电压、多模式、多协议的组合,角点数量直接暴增到上万,某些方案超过12,000个角点,还要覆盖掉电态和零伏态。对应的,.LIB建模的精度要求提高许多,这工作量不是简单加人就能解决的,是真正的工程难题。

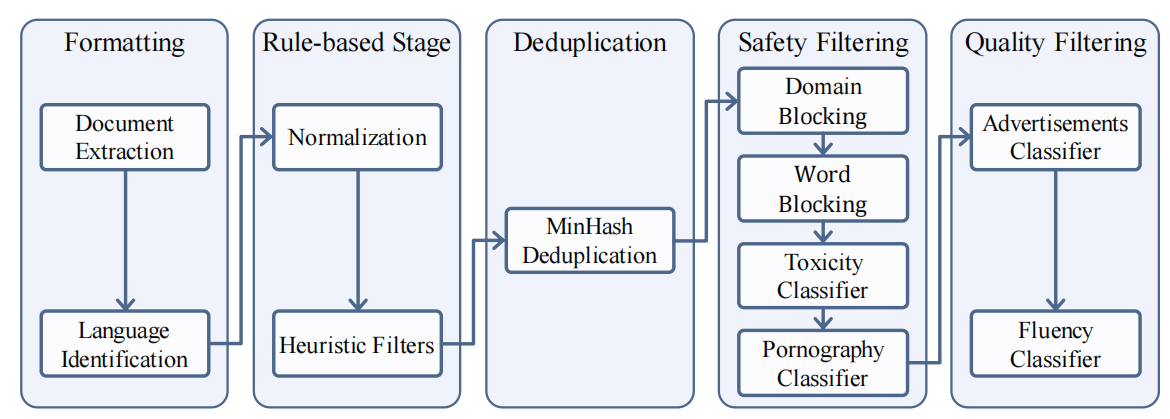

回到论坛本身,发言的专家强调了一个观点:I/O不只是“引脚”的事,而是系统设计的一部分。厂商不再把I/O当成可选项打包给你,而是把它做成多套可选库,按市场、按功耗、按ESD能力来区分。台积电在OIP里把这些库形式化,让客户在流片前就能选到较合适的版本,目的很明确——缩短开发周期,降低返工风险。

细节上,现场还讨论了多协议切换的实现:可配置的输出驱动器、不同模式下的上拉下拉策略、以及高速模式下的上升下降时间控制等。测试点设计、版图对齐、以及封装终端匹配,都是实际落地必须解决的问题。现场案例里有工程组分享了把一颗芯片同时做汽车CAN和手机I3C支持的经验,里面讲到软硬件协同配合的调试流程,和最终在量产前被迫增加的验证场景,听着挺扎心,但也很真实。

一句话:目前做I/O,得更早思考应用场景,库的选择、封装方案、验证策略,都得从系统级出发来决定。看完这波讨论,你会感觉半导体I/O已经从零件级的事情,变成了产品级的权衡题。顺便提醒一下,公众号记得加星标⭐️,第一时间看推送不会错过。

相关文章