输入信号信噪比(SNR)越大,获得的偏振角随时间波动越小;

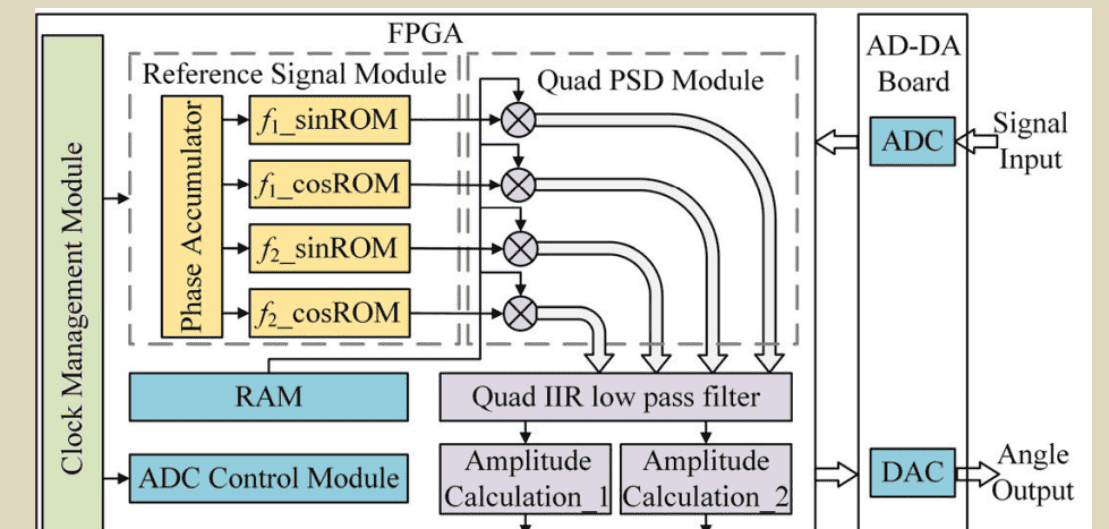

在该系统中,ADC模块负责将采集到的模拟信号转换为数字信号,然后将数字信号传输到FPGA模块。DAC模块将来自FPGA模块的偏振角数字形式转换为模拟信号并通过电压信号输出。

作为基于DLIA系统的核心部分,FPGA模块扮演着执行PSD以及控制ADC和DAC模块的角色。其中,PSD是FPGA模块的核心功能。具体来说,ADC模块传输的数字信号和参考模块生成的参考信号同时输入到一个四通道PSD模块,在其中进行参考信号和来自ADC模块信号的乘法运算。相乘后的信号然后经过四通道IIR LPF滤波,随后进行幅度计算和角度计算。

从混频信号中提取特定频率信号的幅度会受到各种来源的误差影响,例如来自前端放大器的噪声、数字采样的位数以及滤波器的参数设置。其中IIR的部分:较大的时间常数改善了噪声抑制,但导致对快速变化信号的响应时间较长。

硬件部分

根据奈奎斯特采样定理,ADC模块的采样率必须大于600 kSPS,并且其分辨率应尽可能高。

当处理时钟频率为50 MHz时,FPGA的内部处理时间为240 μs,ADC的采样时间为0.24 μs,DAC的转换时间为0.6 μs。因此,系统完成一个偏振角测量周期的总时间为260.84 μs,这意味着基于DLIA的系统满足了MSE诊断对毫秒级工作周期的要求。

关于FFT加窗问题

其本质是要解决信号截断导致的频谱泄露问题;

FFT 本质上是对 “有限长度的时域信号” 进行频域转换,但它有一个隐含前提:输入的有限信号是 “无限长周期信号” 的一个完整周期。同时要满足奈奎斯特采样定理;

但实际中,我们截取的信号几乎不可能恰好是 “整数个周期”—— 比如截取 1 秒的 50Hz 正弦波(1 个周期是 0.02 秒),1 秒刚好是 50 个周期,这没问题;但如果截取 1.01 秒,就包含 50.5 个周期,此时信号的 “开头” 和 “结尾” 幅度不连续(开头为 0,结尾不为 0)。

这种 “非整数周期截断” 会导致:

FFT 会误认为这个 “截断信号” 是 “无限重复的周期信号”,而重复的信号在衔接处会出现 “跳变”(类似方波的突变)。根据傅里叶变换的性质,突变信号会分解出大量高频分量,导致原本单一频率的信号,其能量在频谱上 “扩散” 到相邻频率,形成 “拖尾”—— 这就是频谱泄漏。

窗函数是一种 “两端平滑衰减到 0” 的加权函数(如汉明窗、汉宁窗)。给信号加窗,相当于:

对截断的信号进行 “平滑处理”,让其开头和结尾的幅度自然衰减到 0,避免跳变,从而让信号更接近 “无限周期信号的一个完整周期”

当转换到频域时,原信号的傅里叶变换X(f)不再是冲击峰,而是变成了 “主瓣 + 旁瓣” 的形状(主瓣对应原频率f0,旁瓣就是 “拖尾”)。想让旁瓣衰减大(减少泄漏),往往要接受主瓣变宽(牺牲分辨率);想让主瓣窄(提高分辨率),就要承受旁瓣高(泄漏严重)—— 这是窗函数的固有特性,源于傅里叶变换的 “不确定性原理”(时域信号越平滑,频域能量越分散;时域信号越陡峭,频域能量越集中,但旁瓣越突出)。

线性度测试

设计的基于DLIA系统在幅度解调方面的线性度。在此测试中,信号发生器生成一个固定频率为50 kHz的正弦信号作为设计的基于DLIA系统的输入信号,并将其幅度从0.5 V设置为5.0 V,然后记录系统的幅度解调结果。

聚焦直流超导量子干涉器件(dc-SQUID) 与锁相磁通锁定回路(FLL) 的结合应用,核心是定量分析锁相放大器中调制器 – 解调器相位差对系统响应的影响,为高性能 dc-SQUID 系统设计提供理论与实验依据。

1. dc-SQUID 的特性

优势:高分辨率磁通量传感器,可检测 0.01~100kHz 的磁通信号,分辨率远超其他器件,广泛用于地球物理、材料磁化率测量、生物磁传感(如脑科学)、低电平直流电流检测(电流→磁通→dc-SQUID 检测)。缺陷:固有动态范围窄、线性度差,无法直接满足实际应用需求。

2. 锁相磁通锁定回路(FLL)的作用

通过 FLL 配置让 dc-SQUID 在平衡点附近运行,将其转化为「线性误差信号检测器」,从而:

改善线性度;拓宽动态范围;结合锁相技术抑制噪声,实现高信噪比。

3. 研究核心问题

传统分析忽略锁相放大器中调制器与解调器的相位差 δ(实际无法理想为 0),且未定量分析该相位差对系统稳定性、传递增益的影响。本文推导系统响应与相位差的关系,并实验验证。

调制阶段:输入磁通 I₁(通常是低频 / 直流信号,如待测磁场对应的磁通)与高频调制磁通(ΦmS₁(t),频率 fm)叠加,形成 “高频调制信号”(相当于把 I₁“搭载” 在 fm 上传输,避开低频噪声);解调阶段:锁相放大器的解调器(S₂(t))与调制器(S₁(t))同步(相位差 δ),通过 “高频调制信号 × 同步解调信号 S₂(t)” 的运算,再经过低通滤波器(LPF) 滤除高频分量(如 2fm、fm 等),最终输出的是与输入磁通 I₁成正比的低频 / 直流信号(误差信号的放大版)。

可以用 “恒温系统” 类比:

输入磁通 I₁ = 目标温度(比如 25℃);dc-SQUID 超导环 = 测温传感器(感知当前温度);提取的信号 = 温度误差(当前温度 – 25℃);反馈磁通 Φf = 空调的制冷 / 制热量;

LIA研究1–基于 CIC 的数字正交锁相放大器的甲烷检测

多速率信号处理架构的应用:

传统数字锁相放大器的低通滤波器(LPF)通常在固定的高采样率下工作,计算量大,且要设计一个截止频率极低、过渡带陡峭的FIR滤波器非常困难,需要极高的阶数。

本文创新性地将 级联积分梳状(CIC)滤波器 作为抽取滤波器 与 FIR整形滤波器 结合,引入数字正交锁相放大器(DLIA)中。CIC滤波器先进行高效的降采样(抽取),大幅降低数据速率,再由FIR滤波器在较低的采样率下进行精细滤波。这极大地降低了后续滤波器的设计难度和系统的整体计算量,是实现高精度实时处理的关键。

噪声抑制性能的显著提升:

文章通过实验证明,这种CIC+FIR的滤波器组合相比传统LPF,将提取的二次谐波信噪比(SNR)从38.61 dB提升至44.95 dB,提升了6.34 dB。信噪比的提升直接意味着锁相放大器核心性能——微弱信号检测能力的飞跃。

与浓度反演算法的深度耦合:

锁相放大器的最终输出是用于浓度计算的谐波信号。本文没有将LIA视为一个独立的“黑箱”,而是将其后端的浓度反演算法(NIPALS-ELM)作为整个检测系统的一部分进行优化。LIA提供更干净、更稳定的信号,为高级算法发挥其优势奠定了基础,最终实现了从“信号提取”到“浓度输出”全链条的精度优化。

本文采用的数字正交锁相放大器(DLIA) 工作原理如下:

正交解调:

低通滤波(本文的创新核心):

CIC滤波器的角色:

CIC滤波器是一种无乘法的滤波器,仅由积分器和梳状器组成,结构简单,计算效率极高,非常适合作为抗混叠抽取滤波器,工作在降采样前的第一级。

它将高速采样的数据流降至一个合理的较低速率,从而允许后级的FIR滤波器以更低的阶数实现非常尖锐的截止特性,最终高效地提取出直流分量。

深入研究与可改进之处

滤波器参数的优化空间:

文章提到了使用CIC和FIR,但未详细披露CIC的阶数、级数、抽取因子以及FIR滤波器的具体设计参数(窗函数类型、截止频率、纹波系数等)。这些参数的优化是锁相放大器性能进一步提升的关键,可以作为一个深入研究的方向,例如采用自适应滤波算法动态优化参数以适应不同的噪声环境。

参考信号相位的自适应跟踪:

文中使用的正交锁相放大器虽然避免了显式的移相器,但其性能依然依赖于参考信号与待测信号频率的严格同步。在实际系统中,激光器驱动或气体变化可能导致微小频偏或相位漂移。可以深入研究基于PLL(锁相环)或Costas环的动态相位跟踪技术,使参考信号能自动跟踪输入信号的相位变化,进一步提升系统的鲁棒性。

多谐波同时提取与处理:

WMS技术中,不仅二次谐波(2f)包含浓度信息,一次(1f)、四次(4f)谐波等也可用于归一化、线型修正和压力补偿。目前的DLIA结构稍作扩展(增加乘法器和滤波器通道)即可同时提取多阶谐波。后续研究可以设计多通道并行处理的DLIA,综合利用多谐波信息,极大提升检测系统的准确性和抗干扰能力。

系统集成与实时性实现:

本文系统使用了STM32和DSP两片处理器。一个深入的研究方向是利用FPGA 的高度并行性,将CIC滤波、FIR滤波、乘法器、甚至NIPALS的部分预处理算法全部集成在单一芯片中实现,构建一个真正的片上系统(SoC) 锁相放大器,这将极大提高系统的速度、可靠性和集成度。

更广泛的适用性验证:

本文出色地验证了该系统在甲烷检测上的性能。其锁相放大器设计的普适性值得在更广泛的场景中验证,例如不同调制频率、不同噪声背景(工业现场、车载平台等)下的性能表现,以证明其不仅是一个“甲烷检测专用”锁相放大器,而是一个高性能的通用微弱信号检测平台。

LIA研究2–Evolution of Lock-In Amplifier as Portable Sensor Interface Platform: A Review

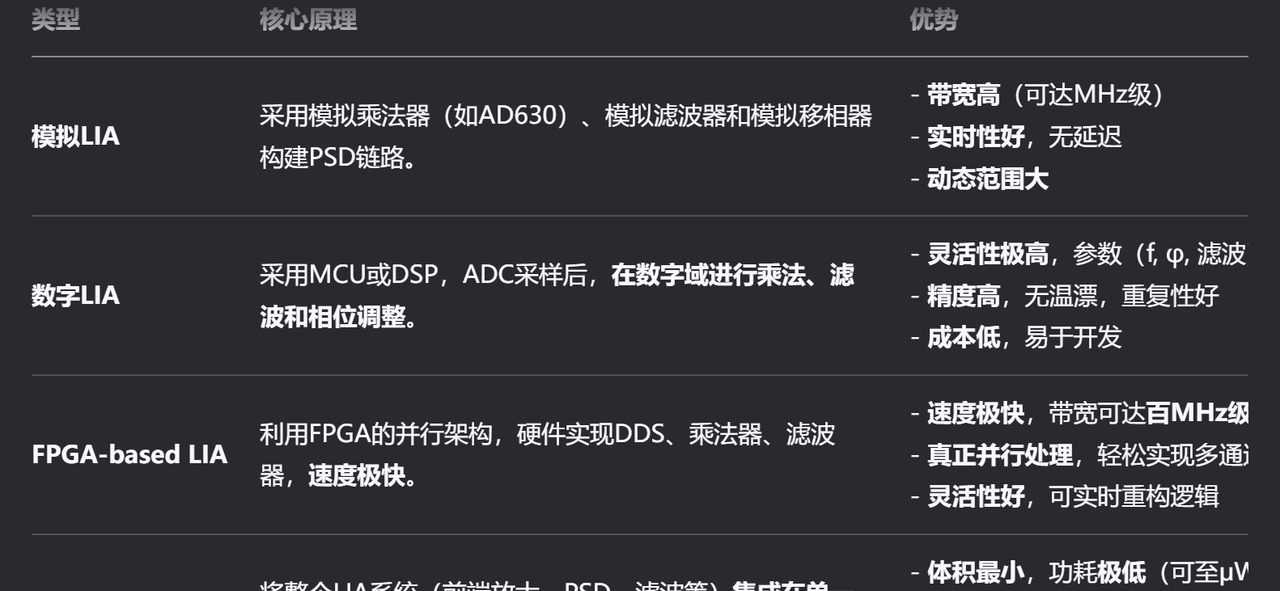

数字和FPGA实现的LIA在高频、多通道应用中表现优异,而CMOS集成LIA在低功耗、微型化方面更具优势。

嵌入式设计侧重于全模拟和混合设计拓扑,以实现低电压、低功耗的便携式传感器应用。基于FPGA的LIA设计利用专用乘累加单元、处理器、DDS和高速ADC/DAC模块,发挥了数字实现的优势。LIA的集成CMOS设计侧重于实现低电压、低功耗的专用片上实现。

LIA的实现技术分类

模拟LIA:传统结构,适用于低频低噪声场景

数字LIA:基于DSP/微控制器,灵活性强

FPGA-based LIA:高频、多通道、实时处理

CMOS集成LIA:低功耗、微型化、适合便携设备

随着与嵌入式设计集成的趋势,重点是实现高速便携式的相敏检测。对于嵌入式应用,方波输入信号是相当直观的选择,而不是传统的正弦参考。

方波的 “信号处理逻辑” 更简单,降低嵌入式的 “算力负担”

相敏检测的核心是 “让参考信号与被测信号‘同步’,从而提取出特定频率的有用信号”(比如 WMS 技术中的 1f、2f 谐波)。方波的特性让这个 “同步处理” 过程变得异常简单:

方波只有 “高 / 低” 两种电平(或 “正 / 负” 两种极性,比如 ±5V 方波),对应的数字信号就是 “1/0”—— 嵌入式系统处理时,不需要复杂的乘法、三角函数计算,只需要判断 “当前时刻参考信号是高还是低”,再与被测信号(经过 ADC 转换的数字量)做简单的 “乘法”(其实就是 “同极性时保留信号、反极性时翻转信号”,本质是 “解调”)。

举个例子:假设被测信号里有 10kHz 的有用信号(和其他频率的噪声),参考方波也是 10kHz。当参考方波为 “高” 时,我们直接保留被测信号的当前值;当参考方波为 “低” 时,我们把被测信号的值取反 —— 这个过程相当于 “筛选” 出了和参考频率一致的有用信号(噪声因为频率不同,会被后续低通滤波滤掉)。整个处理过程用几句代码就能实现,占用的算力极少,嵌入式芯片(哪怕是低成本单片机)都能轻松应对。

在处理阻抗传感器时,LIA设计包含一个可调移相器,该移相器产生一个与传感器相位正交的参考信号。这使得能够进行完美的相移检测以提取传感器信号。

光学领域的信号检测至关重要,并面临从光学隔离、环境干扰、器件噪声和热噪声等问题带来的挑战。增加其关键性的是,通常来自传感器的光学信号幅度低,并且通常分布在宽频带中。锁相放大器非常适用于热成像

核心原理:相敏检测(PSD)

所有LIA的核心都是相敏检测(Phase-Sensitive Detection),也称为零差检测(Homodyne Detection)。其基本原理可概括为:

调制:用一个特定频率的正弦或方波信号来激励传感器。

相乘:将传感器的响应信号(包含有用信号和大量噪声)与一个同频率的参考信号相乘。

滤波:相乘的结果会产生一个直流(DC)分量和一个在 2f附近交流(AC)分量。其中的直流分量正比于输入信号的幅度及其与参考信号相位差的余弦值。通过一个低通滤波器(LPF)滤除所有高频交流成分和噪声,最终只输出这个稳定的直流信号。

这个过程极大地将信号的检测带宽压缩到一个极窄的窗口(围绕 f_ref),从而几乎只让与参考频率同频的信号通过,有效地抑制了所有带外噪声,实现了极高的信噪比(SNR)提升。

文献在讨论与结论部分指出了多个未来值得深入研究的方向:

更高程度的集成化与微型化:

方向:将传感器本身与CMOS接口电路(包括LIA)实现单片集成(Monolithic Integration)。

意义:这是实现终极“智能传感器”的关键。可以极大减少寄生效应,提高整体性能、可靠性和便携性,为植入式生物传感器和大规模传感器网络铺平道路。文献中Vijay [85] 的59,760电极细胞阻抗成像芯片是这一方向的典范。

算法优化与智能化:

方向:研究更低计算复杂度、更高效率的数字锁相算法,以降低对处理器性能和功耗的要求。

具体方法:利用参考信号的对称性减少运算量 ;采用随机采样、过采样等技术优化信噪比和速度;甚至探索引入机器学习算法对输出信号进行智能后处理,以进一步提取特征和抑制噪声。

多通道与多功能融合:

方向:发展高度集成的多通道LIA系统,能够同步测量多个传感单元。

意义:这对于生物医学应用(如脑电、肌电、细胞阻抗成像)和环境监测(传感器阵列)至关重要。FPGA和先进CMOS工艺是实现这一目标的主要技术路径 [29, 69, 85]。

动态性能与自适应能力提升:

方向:增强LIA应对动态信号的能力。例如,开发更快速的自动相位跟踪算法 [41],以应对传感器响应相位可能变化的情况(如在活体检测中)。

改进:虽然已有自动相位对准的模拟方案 [52],但在数字域实现更快速、更精确的自适应算法是未来的趋势。

偏移补偿与动态范围优化:

方向:集成更有效的偏移消除(Offset Cancellation) 技术 [68]。

意义:许多传感器(如生化FET传感器)存在巨大基线偏移,会饱和LIA的前端。通过差动测量、虚拟补偿电路等技术主动抵消偏移,可以充分利用LIA的动态范围,检测微弱的相对变化信号。

面向极端环境的可靠性设计:

方向:虽然文献提及较少,但开发能在高温、高辐射、高湿度等恶劣环境下稳定工作的专用LIA接口电路也是一个重要方向。这需要对材料和电路拓扑进行特殊设计。

LIA研究3–Lock-in amplifiers as a platform for weak signal measurements: Development and applications

评估了其在阻抗测量、光学检测、电化学分析、热学传感和生物传感等多个领域的多样化应用

技术路径多样化:不存在“唯一最优”的LIA架构。模拟LIA在高速、低功耗、高带宽方面有优势;数字LIA灵活性高、稳定性好;混合LIA结合二者优点;软件LIA及基于FPGA/微控制器的实现则降低了成本和门槛,促进了普及和创新。

性能持续优化:通过算法创新(如过采样、随机采样、自动相位追踪)、电路设计优化(如电流域处理降低功耗)、系统集成(如CMOS单片集成)和频率扩展技术(如随机处理突破奈奎斯特限制),LIA的性能边界在被不断推动。

一、为什么 “ADC 和处理器发展能提全数字 LIA 带宽,混合架构仍适合超高频”?

先明确一个前提:全数字 LIA 的核心是 “用数字电路做所有相敏检测工作”(比如信号采样、与参考信号相乘、滤波、提取幅值 / 相位),而这些工作的 “速度上限”(即带宽),完全受制于两个关键器件:ADC(模数转换器)和处理器(如 FPGA、DSP)。

1. ADC 和处理器发展 → 全数字 LIA 带宽提升

全数字 LIA 要处理更高频率的信号(比如从 10MHz 升到 100MHz),需要解决两个问题:

ADC 得 “跟得上” 高频信号:ADC 的核心指标是 “采样率”—— 要采集高频信号,必须满足奈奎斯特定理(采样率≥2 倍信号最高频率,实际会留 1.5~2 倍余量)。比如以前 ADC 最高采样率只有 200MHz,最多能处理 100MHz 的信号;现在 ADC 技术发展,采样率能到 2GHz,就能处理 1GHz 的高频信号了。处理器得 “算得快”:LIA 的核心操作是 “信号与参考信号相乘”“数字滤波”(比如 FIR/IIR 滤波),这些都是计算密集型任务。以前处理器(比如早期 DSP)算力弱,处理 10MHz 信号的乘法 / 滤波都要卡半天;现在 FPGA(现场可编程门阵列)或高端 DSP 的算力翻了几百倍,能实时完成高频信号的数字运算,不会让 “计算速度” 拖慢信号处理的节奏。

简单说:ADC 是 “耳朵”(听得见高频声音),处理器是 “大脑”(能快速理解高频声音),两者都变强了,全数字 LIA 自然能处理更高带宽的信号。

2. 混合架构 → 解决超高频(>100MHz)测量的 “性价比难题”

全数字 LIA 在超高频(比如 200MHz、1GHz)场景下会遇到一个死穴:超高速 ADC 太贵、太费电。

比如要测 200MHz 的信号,按奈奎斯特定理,ADC 采样率至少要 400MHz,实际工程中为了避免混叠,可能需要 800MHz 甚至 1GHz 的 ADC—— 这种 ADC 不仅成本是普通 ADC 的 10~100 倍,功耗也会飙升(比如从几十毫瓦到几瓦),对于便携式、低功耗设备(如手持传感仪)完全不现实。

而混合架构(模拟 + 数字)的思路是 “分工合作”:

先用「模拟电路」做 “预处理”:比如用模拟乘法器(比数字乘法器快得多)先将超高频信号与一个 “参考高频信号” 混频,把原信号的频率 “降下来”(比如 200MHz 信号混频后变成 1MHz 的 “中频信号”);再用模拟低通滤波器滤掉高频杂波。再用「数字电路」做 “精细处理”:经过模拟预处理后,信号频率已经降到很低(比如 1MHz),此时用普通的、低成本的 ADC(采样率 2~4MHz)就能采样,后续处理器也能轻松完成数字滤波和相位提取。

类比:就像你要搬一个 100 斤的箱子(超高频信号),直接用手搬(全数字)太累;先找个滑轮组(模拟预处理)把重量减到 10 斤,再用手搬(数字处理)就轻松多了。所以超高频场景下,混合架构是 “用模拟的‘快’补数字的‘贵’”,性价比更高。

二、为什么 “随机采样能打破奈奎斯特采样定理的限制”?

首先要纠正一个误区:随机采样不是 “推翻” 奈奎斯特定理(物理规律不会被打破),而是用 “随机采样 + 数学重构” 的方式,绕开了奈奎斯特对 “固定采样率” 的要求,实现 “低速 ADC 测高频信号”。

1. 先懂奈奎斯特定理的 “固定采样” 局限

奈奎斯特定理的核心是 “固定时间间隔采样”—— 比如每隔 1 微秒采一次(采样率 1MHz),这种固定间隔就像 “用一把固定齿距的梳子梳信号”:如果信号频率太高(超过采样率的一半),梳子的齿就会 “漏过” 信号的关键信息,导致 “混叠”(比如把 1.2MHz 的信号错看成 0.2MHz)。

问题在于:如果要测 1GHz 的高频信号,按固定采样得用 2GHz 以上的 ADC—— 但这种 ADC 可能比整个设备还贵,根本不实用。

2. 随机采样的 “破局思路”:不按固定间隔,靠 “概率” 覆盖高频信息

随机采样的核心是 “不固定采样时间”—— 比如这次隔 0.5 微秒采,下次隔 1.2 微秒采,再下次隔 0.8 微秒采,采样时间完全随机,但会采足够多的点(比如几万、几十万次)。

为什么这样能测高频信号?

举个例子:要测一个 1GHz 的正弦波(周期 1 纳秒),用采样率 100MHz 的 ADC(固定间隔 10 纳秒,远大于信号周期,按奈奎斯特肯定不行)。但如果随机采样 10 万次:

虽然每次采样的时间是乱的,但总会有一些采样点 “刚好” 落在正弦波的波峰、波谷、过零点等关键位置(概率上能覆盖信号的所有相位和幅度);之后用专门的 “重构算法”(比如基于压缩感知理论),把这些随机散落的 “关键点点” 拼起来,就能还原出原本 1GHz 的高频信号波形。

类比:就像你要画一条快速移动的蛇(高频信号),如果固定每秒拍 1 张照(固定采样),蛇动太快会拍糊;但如果随机拍 1000 张(不管间隔多久),总会拍到蛇的头、身体、尾巴的关键位置,最后把这些照片拼起来,就能还原蛇的完整形态。

本质上,随机采样是 “用‘更多的采样次数’和‘更聪明的算法’,替代了‘更高的固定采样率’”,从而用低速 ADC 实现了高频信号的测量,特别适合低成本、低功耗的场景(比如便携式高频传感器)。

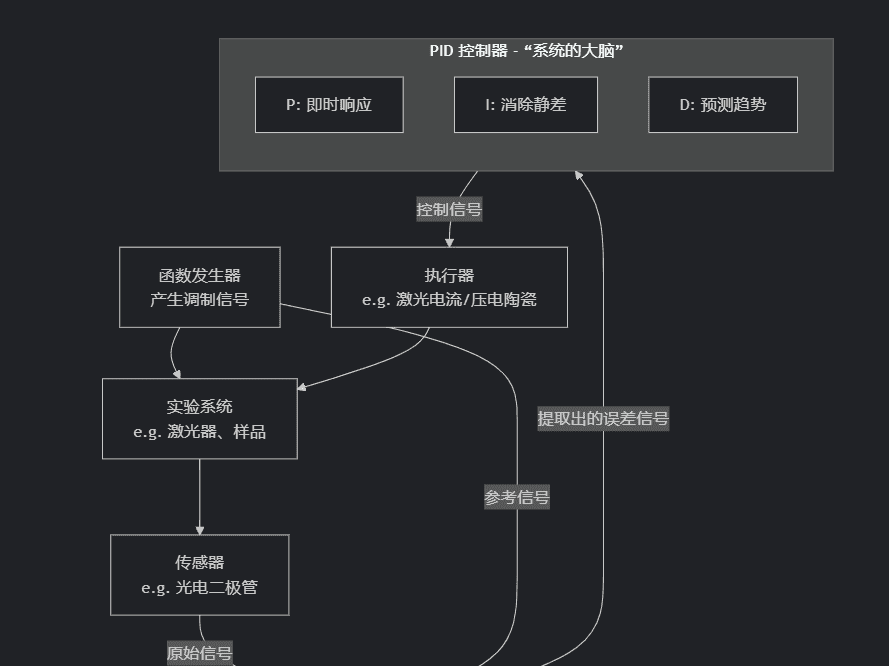

LIA研究4–An FPGA based all-in-one function generator, lock-in amplifier and auto-relockable PID system

固件设计(VHDL):

函数发生器:DDS方式生成正弦、方波、三角波、锯齿波;

锁相放大器:数字混频 + 高阶低通/高通滤波器;

PID控制器:三种类型(A/B/C)可选,支持双级PID(DC/AC耦合);

自动重锁算法:失锁后自动扫描寻找信号并重新锁定。

可改进方向

提升ADC/DAC性能:

采用16-bit或更高分辨率ADC,提升灵敏度;

使用更高速的SPI或USB接口替代UART。

优化滤波器设计:

引入自适应滤波器或FIR滤波器,进一步提升滚降性能和相位一致性。

增强自动重锁智能性:

引入机器学习算法识别信号特征,适应多峰或非理想信号;

增加手动/自动模式切换,提供更多控制自由度。

扩展应用接口:

提供API接口,支持LabVIEW、MATLAB等平台调用;

增加网络模块,支持远程Web控制。

功耗与体积优化:

采用更小尺寸的FPGA或SoC方案,适合嵌入式或便携式应用。

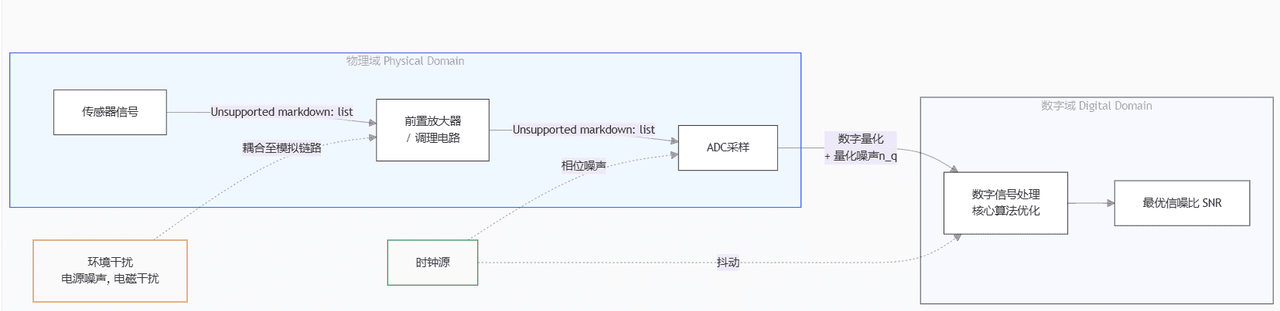

一、深入噪声源分析与建模(基础)

首先,必须定量或定性地了解噪声来自哪里。这是所有优化工作的前提。

前端模拟电路噪声:

研究内容:建立输入级的噪声模型。包括:

热噪声 (Johnson-Nyquist Noise):与电阻、带宽和温度直接相关。

√(4kTRB)

运放噪声:包括电压噪声密度

(nV/√Hz)

(pA/√Hz)

1/f 噪声:低频噪声,影响低频率测量的性能。

方法:使用SPICE仿真软件(如LTspice)对模拟前端电路进行噪声仿真,确定理论噪声下限。

量化噪声:

研究内容:ADC将模拟信号离散化带来的固有噪声。噪声功率 =

q²/12

q

方法:建模分析如何通过 提高ADC位数(如从12位提升至16位或18位)和 过采样(Oversampling) 来降低量化噪声。过采样结合降采样可将量化噪声分布在更宽的频带上,再通过数字低通滤波滤掉带外噪声,有效提高信噪比和有效位数(ENOB)。

时钟抖动(Jitter)噪声:

研究内容:ADC采样时钟的不稳定性会导致采样时刻 uncertainty,在高频信号下转换为严重的幅度噪声。

方法:分析时钟抖动与SNR的关系:

SNR = -20log10(2π × f_in × t_jitter)

数字算法噪声与误差:

研究内容:数字处理(如乘法、滤波)中的舍入误差(Round-off Error) 和截断误差(Truncation Error)。在定点数FPGA实现中,数据位宽的选取至关重要。

方法:通过位宽增长(Bit Growth) 策略和饱和处理(Saturation) 来管理这些误差,避免极限环振荡。

二、数字信号处理算法优化(核心)

这是数字锁相放大器噪声优化的主战场。

滤波器优化设计:

研究内容:

滤波器类型:比较FIR(有限长单位冲激响应)和IIR(无限长单位冲激响应)滤波器的优劣。FIR可以提供严格的线性相位,避免信号失真;IIR可以用较低的阶数实现更陡峭的滚降,但需注意相位非线性。

滤波器阶数与滚降:如文献所述,更高阶的滤波器提供更陡的滚降,能更有效地抑制带外噪声。研究阶数对计算资源和噪声抑制效果的权衡。

滤波器带宽:在保证信号完整性的前提下,尽可能窄的滤波器带宽是抑制噪声最有效的手段。研究如何根据信号频率自动适配带宽。

方法:使用MATLAB或Python的

scipy.signal

多周期平均与降采样:

研究内容:在滤波器之后,对输出进行多周期平均(本质是一个移动平均滤波器),可进一步平滑噪声,提高测量精度。

方法:在FPGA中实现一个累加器和一个计数器,实现同步积分(Sync Integration)的效果。

高动态范围技术:

研究内容:当需要同时测量很大和很小的信号分量时(如高次谐波),对ADC的动态范围要求极高。

方法:研究∑-Δ ADC的应用,其通过极高的过采样率和噪声整形技术,将量化噪声推向高频,从而在低频段获得极高的有效位数和动态范围。

三、FPGA实现层面的优化(工程关键)

资源与精度权衡:

研究内容:在FPGA中,数字的表示方式(定点数 vs. 浮点数)、乘法器/DSP块的使用策略,直接影响噪声性能和资源消耗。

方法:采用定点数仿真,精确分析每一步操作的位宽,在保证足够信噪比的前提下,找到最优的位宽分配方案(如文献中的表1),节省FPGA资源。

同步设计:

研究内容:确保参考信号生成、ADC采样、数字混频、滤波等所有环节严格同步,避免因异步操作引入额外的抖动和噪声。

方法:使用FPGA内部的全局时钟网络和可靠的时钟管理策略。

四、后续可研究的具体方向

自适应滤波:研究基于LMS/RLS算法的自适应滤波器,使其能自动跟踪信号频率的微小变化,实时调整滤波器参数,始终保持最优信噪比。

相关平均:在时域进行多次扫描的同步累加,能极有效地提高信噪比(SNR ∝ √N)。

先进降噪算法:探索将小波变换(Wavelet Transform) 等现代信号处理技术用于噪声滤除,特别适用于非平稳信号。

硬件升级与协同设计:与电路设计者合作,设计专用的低噪声模拟前端ASIC或PCB,与FPGA数字处理核心进行协同优化,实现性能的终极提升。

LIA研究5–Many-Body Quantum Lock-In Amplifier

本文提出一种基于多体多脉冲量子干涉的 “纠缠增强型量子锁相放大器” 方案:通过在信号探测阶段施加周期性 π 脉冲序列,实现多体量子锁相放大;通过选择合适的输入量子态(如自旋猫态)和读出操作,可同时提取未知交流场的频率与幅度(基于粒子数测量);锁相点可通过单次探测的信号对称性或多次探测的时间平均信号确定,且锁相点的测量信号与探测时间无关。特别地,当输入自旋猫态并采用基于相互作用的读出操作时,频率与幅度的测量精度均可接近海森堡极限(HL);此外,该多体量子放大器对强随机噪声具有鲁棒性。本文为多体量子系统测量时变信号提供了新路径,也为实现交流信号的海森堡极限检测提供了可行方法。

阶数选择的核心逻辑:“够用即止”,避免盲目追求高阶 ——

若仅需初步去噪(如电源纹波):选一阶;若需平衡性能与成本(如多数工业传感器):选二阶(Butterworth 型优先,通带平坦);若需强干扰抑制(如医疗 / 射频):选 3~10 阶(根据抑制需求确定,如需 10⁴倍抑制选 4 阶,10⁶倍选 6 阶)。

有源 vs 无源的选择:

低频信号(<100kHz)、带负载需求:选有源滤波(如 Sallen-Key);高频信号(>1MHz)、无供电条件:选无源 RLC 滤波(或 LC 多阶)。

模拟 vs 数字的选择:

实时性要求高、信号频率低(<1MHz):选模拟多阶(无计算延迟);需严格线性相位、信号频率高(>1MHz):选数字多阶(如 FIR 滤波,通过 FPGA 实现并行计算)。

LIA研究6–Research on weak signal detection of integral average digital lock-in amplifier

针对传统数字锁相放大器(DLIA)在强噪声背景下检测微弱信号时需极低截止频率低通滤波器(LPF)导致输出失真与波动大的问题,提出了一种基于积分平均数字锁相放大器(IADLIA) 的微弱信号检测方法。该方法基于互相关检测理论,用积分平均模块替代传统LPF,显著提高了检测精度与输出稳定性,并在轴承故障诊断中验证了其有效性。

IADLIA无需复杂LPF设计,结构更简单;

在强噪声环境下(SNR低至-32 dB),IADLIA仍能稳定、准确地检测幅值与相位;

输出MSE可低至10−5 μV210−5μV2,标准差远低于传统DLIA;

在轴承故障诊断中,能有效提取故障特征频率,抗干扰能力强于传统方法。

不足之处

目前仅针对周期性信号,对非平稳/非周期信号的研究尚未深入;

IADLIA的输出稳定时间较长,需进一步优化;

多频率信号检测能力仍有提升空间;

实验数据虽来自标准数据库,但实际工业环境的复杂性未充分模拟。

后续可改进方向

扩展至非平稳/非周期信号:结合时频分析方法(如小波变换、EMD);

优化积分平均算法:引入自适应积分时间控制,缩短稳定时间;

多频率同步检测:开发多通道IADLIA,支持多频信号同时提取;

硬件实现与嵌入式系统集成:基于FPGA或DSP实现实时IADLIA系统;

结合深度学习:用于自动特征提取与故障诊断,提升智能性。

LIA研究7–A Novel Digital Lock-In Amplifier With Extended Lyapunov Demodulation for Wide Dynamic Range Applications

该文针对宽动态范围(DR)测量需求,提出一种基于扩展Lyapunov解调(ELD)算法的数字锁相放大器(DLIA)。通过自动增益控制(AGC)调节激励信号幅度,实现灵敏度动态调整,无需额外硬件。ELD算法能在解调过程中同步进行灵敏度补偿,确保在DR切换时信号提取的连续性与准确性。系统在FPGA平台上实现,电压检测DR达226.2 dB,电容检测DR达194.3 dB,适用于高精度宽动态范围测量。

提出ELD算法,将增益补偿融入解调过程,实现无缝灵敏度调整;

通过AGC调节激励幅度,避免使用外部可变增益放大器,降低系统复杂度;

系统具有LTI特性,保证了解调过程的稳定性和一致性;

在FPGA上全数字实现,具备高灵活性与可重构性;

在电容检测等实际应用中验证了宽动态范围与高精度。

不足之处

系统对相位噪声敏感,尤其在极低信号幅度下;

ELD算法需动态调整自适应参数γ,计算复杂度较高;

目前仅验证了周期性信号,对非平稳信号适应性未研究;

实验环境较为理想,工业现场干扰未充分模拟。

后续可改进方向

抗相位噪声优化:引入相位锁定环(PLL)或卡尔曼滤波提升低信噪比下的稳定性;

多频信号支持:扩展ELD至多频解调,支持频分复用系统;

非平稳信号处理:结合时频分析(如小波变换)处理非平稳信号;

硬件优化:采用更高精度ADC/DAC,提升系统底噪性能;

自适应带宽调整:根据信噪比动态调整解调带宽,提升实时性;

AI辅助调试:利用机器学习优化AGC和ELD参数,提升系统自适应能力。

LIA研究8–High-Speed processing method for weak Terahertz signals based on Dpll-Booth algorithm

研究问题

太赫兹信号强度弱、易受噪声干扰,传统模拟LIA受外部噪声影响大;

现有数字LIA在处理速度上仍有局限,无法满足高速采集需求;

乘法器运算速度与资源占用成为数字LIA性能瓶颈。

研究方法

系统结构:采用正交矢量型数字LIA结构,包含DDS参考信号生成、Booth乘法器、CIC-FIR滤波器和RMS检测;

算法优化:提出改进的Radix-4 Booth编码乘法器,优化补码电路,减少逻辑延迟;

FPGA实现:在FPGA上实现多通道高速DLIA算法,进行资源与速度分析;

性能评估:通过动态范围、资源占用、运行时间等指标评估系统性能。

创新点

提出基于Radix-4 Booth编码的PSD乘法器,显著提升运算速度;

优化补码生成电路,采用多级OR操作结构,减少逻辑门延迟;

在FPGA上实现多通道高速DLIA,支持多频率信号并行处理;

系统具备高动态范围和低资源占用,适合嵌入式高速信号处理应用。

不足之处

在信噪比提升方面仍有不足,需进一步优化滤波算法;

仅针对周期性信号,未涉及非平稳信号处理;

实验数据量较小(12×12bit,4096点),大规模数据处理能力未验证;

未与其他现代LIA算法(如Lyapunov解调、Kalman滤波等)进行对比。

后续可改进方向

信噪比优化:引入自适应滤波或小波降噪算法;

多频率自适应处理:支持动态频率跟踪与多频信号同步解调;

非平稳信号处理:结合短时傅里叶变换(STFT)或经验模态分解(EMD);

硬件加速:采用更高系列FPGA(如UltraScale+)或集成AI加速核;

系统集成:与太赫兹光源、探测器集成,实现片上系统(SoC);

算法对比研究:与Lyapunov、Kalman等现代解调算法进行对比分析。

LIA研究9–Lock in Amplification and Synchronous Detection Based on Arduino

尽管本文是一个低成本演示,但基于此架构,我们可以提出一系列切实可行的改进方案:

平台升级(最直接的改进):

换用更强大的32位Arduino(如Arduino Due、ESP32、STM32系列),它们具有更高的主频、硬件FPU、更多内存和更高精度的ADC,可以轻松实现更高采样率、更复杂滤波器和完善的正交解调。

算法优化:

实现正交解调:增加一路余弦参考信号和乘法器,同时计算I(同相)和Q(正交)分量,即可通过

sqrt(I^2 + Q^2)

atan2(Q, I)

改进滤波器:用更高效的FIR或IIR滤波器替代简单的移动平均滤波,以获得更好的噪声抑制性能。

添加数字AGC:如前一篇文献讨论,可以在数字域实现自动增益控制,扩展动态范围。

硬件优化:

使用外部ADC模块(如16位ADS1115)以获得更高的采样精度和动态范围。

为光传感器添加机械调制盘(Chopper) 进行物理调制,避免LED PWM调制可能带来的谐波问题,并进一步抑制低频噪声。

功能拓展:

开发成开源教学套件,配套详细讲义和实验指南,广泛应用于工程教育。

针对特定低成本应用场景(如室内光照度监测、简单的光电门禁)进行定制化开发。

LIA研究10–A novel microfluidic detection system based on digital lock-in amplifier with high bandwidth and low phase float

传统的LIA流程如下:

1.微信号进入前置放大器(伴随噪声,通常器件为差分放大器)——> 2. 抗混叠/带通预滤波(通常是RC/RLC)——>3. 生成参考信号 ——> 4. 将原微信号交流放大 ——> 5.混频解调——> 6. LPF——> 7.直流放大,增益校准

研究方法

理论建模先行:

基于Maxwell混合理论建立了颗粒/细胞在微流道中的精确等效电路模型(R-C模型)。

建立了完整的LC谐振检测电路模型,深入分析了颗粒通过时如何引起谐振频率偏移,进而导致相位和幅度变化,并从理论上证明相位变化比幅度变化更显著,因此选择相位作为检测量。

自主研发高性能DLIA:

高速模拟前端:采用超低噪声(1.5 nV/√Hz)的全差分放大器(FDA)设计三级放大电路,确保高频下的信噪比。

高速数据转换:采用采样率1 GHz的ADC和DAC,满足奈奎斯特采样定理(用于300 MHz信号)。

创新性数字核心:为解决FPGA主频(250 MHz)低于DAC速率(1 GHz)的矛盾,提出了四路并行DDS结构,通过相位偏移巧妙合成1 GHz的正弦激励信号。

低相位浮动设计:整个系统优化旨在实现高带宽下的低相位噪声和低抖动。

系统集成与验证:

将自主研发的DLIA与自主设计的微流控检测电路(含LC谐振腔和C2V转换器)、 syringe pump集成,构建完整实验系统。

使用Ps微球和酵母细胞作为样本,在24.24 MHz谐振频率下进行实验,并与商用高端LIA(Zurich Instruments HF2LI 和 Sci- Instruments OE2041)进行性能对比。

创新点

应用创新:将LIA技术成功应用于高频(百MHz级)微流控阻抗检测,并实现了基于相位符号的细胞/颗粒区分,为无标记生物检测提供了新方法。

技术创新:自主研发了性能顶尖的高带宽、低噪声DLIA,打破了该性能领域对商用昂贵设备的依赖。

算法/结构创新:提出了四路并行DDS结构,巧妙地在较低FPGA时钟下实现了超高频率信号的生成,解决了高速设计的核心瓶颈。

系统级优化:对整个信号链(从前端FDA到后端处理)进行了协同设计,特别关注相位精度,而不仅仅是幅度,从而实现了极高的检测灵敏度。

后续可改进方向

走向集成化与微型化:

将前端模拟电路(FDA、C2V)和LC谐振电感尝试与微流控芯片进行片上集成,例如采用MEMS技术制造微型电感,可以极大减少寄生参数和噪声,提升系统稳定性和一致性。

提升通量与智能化:

结合机器学习算法对提取出的相位、幅度信号进行实时分析,实现多参数(大小、类型、活性)细胞的自动分类与计数,向真正的智能流式细胞仪发展。

优化数据通路,尝试在FPGA内实现更高速的实时信号处理,减少对上位机的依赖,提升系统响应速度。

拓展应用边界:

将系统应用于更广泛的生物颗粒检测,如外泌体、细菌、病毒等,验证其在各生物医学领域的实用性。

探索在多频率下同时进行测量,获取细胞的阻抗谱信息,从而得到更丰富的生物物理特性。

降低成本与功耗:

研究能否在保持性能的前提下,采用更经济的ADC/DAC方案或新型架构,降低系统成本,促进其普及。

对于便携式应用场景,需优化系统功耗,特别是前端放大器和高速数据转换器的功耗。

flowchart TD A[DDS生成1GHz采样率的<br>正弦激励信号] --> B[功率放大器(PA)<br>驱动微流控芯片] B --> C[颗粒通过微流道<br>引起阻抗变化] C --> D[LC谐振电路<br>(核心的模拟带通滤波器)<br>将阻抗变化转换为电流变化] D --> E[跨阻放大器(C2V)<br>将电流信号转换为电压信号] E --> F[输出功率放大器(PA)<br>缓冲与驱动] F --> G[低噪声全差分放大器(FDA)<br>提供增益并抑制共模噪声] G --> H[1 GHz ADC采样<br>(模拟前端带宽1.5GHz<br>起到抗混叠滤波作用)] H --> I[数字锁相放大器(DLIA)核心<br>进行数字解调与低通滤波] I --> J[输出幅值与相位信息] J --> A

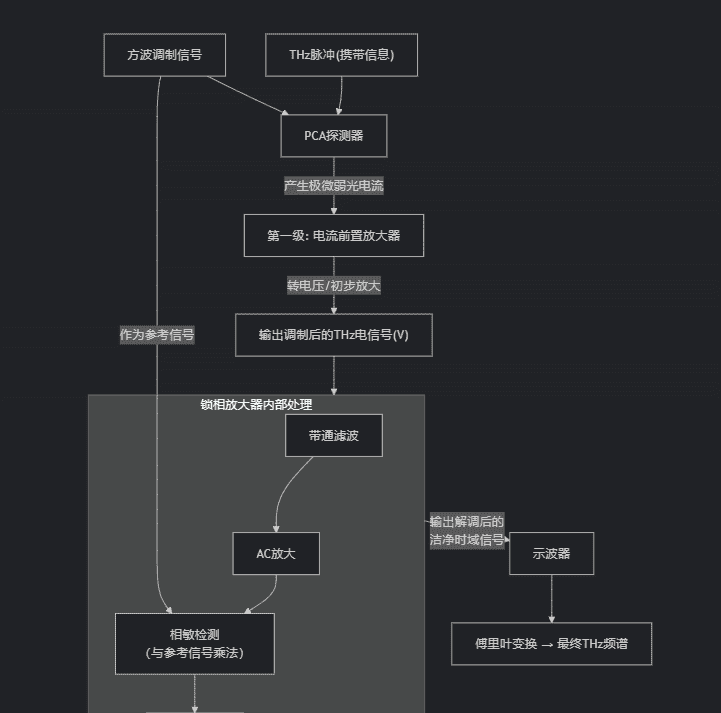

LIA研究11–Terahertz asynchronous optical sampling spectroscopy with lock-in detection

本研究提出了一种结合锁相放大器的太赫兹异步光学采样(THz-ASOPS)光谱系统。通过高压脉冲发生器驱动光电导天线(PCA)发射器,产生调制后的太赫兹脉冲,再经由PCA探测器接收,并通过两级放大(低噪声前置放大 + 数字锁相放大)处理信号。实验结果显示,系统在时域信噪比(SNR)提升3倍,频谱动态范围(DR)提升5 dB。

创新点

首次将锁相检测系统集成于THz-ASOPS中,实现高频调制与噪声抑制。

提出并验证了电调制PCA发射器的方案,替代传统的机械调制。

通过双级放大+锁相处理,显著提升系统信噪比与动态范围。

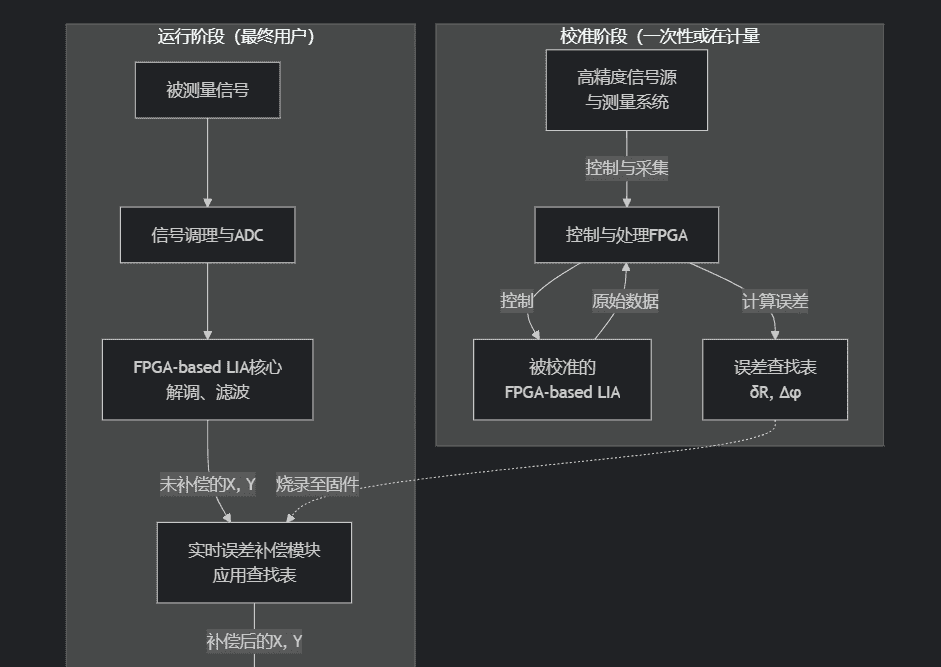

LIA研究12–High-Resolution Real-Time Displacement Measurement for Heterodyne Interferometers Using a Modular Lock-In Amplifier in an FPGA Architecture

本研究提出了一种基于FPGA架构的模块化锁相放大器(LIA),用于外差干涉仪的高分辨率实时位移测量。该系统通过数字信号处理技术,实现了纳米级分辨率(最高达14 nm) 和5200 samples/s的高采样率,适用于高速实时控制应用。系统在模拟和实际测试中均表现出色,无需插值即可达到λ/45的分辨率,优于传统条纹计数法(λ/4)。

创新点

提出LDPD方法,在锁相放大器中引入降采样步骤,优化滤波性能并简化FPGA实现。

开发了完整的FPGA硬件架构,包括信号采集、处理、通信一体化,支持多轴扩展。

实现了高采样率(5200 Sps)与高分辨率(14 nm)的平衡,优于多数现有方案。

系统具有模块化、低成本、可扩展的特点,适合工业嵌入应用。

不足之处

环境因素未补偿:未对温度、气压等环境影响进行校正,可能影响长期稳定性。

验证场景有限:虽然与CENAM标准对比,但测试路径单一(5.5 m线性运动),缺乏多维度验证。

机械误差影响:实验中机械反向间隙(backlash)导致的位置误差未被完全消除。

噪声敏感性:系统在SNR低于50 dB时性能显著下降,依赖前端信号质量。

预印本状态:尚未经过同行评审,部分结论可能需要进一步验证。

后续可改进方向

环境补偿算法:引入温湿度、气压传感器,进行实时环境参数校正。

多轴同步测量:利用FPGA并行能力,同时处理多路干涉信号,适用于多维测量。

自适应滤波与噪声抑制:加入自适应滤波算法,提升低SNR下的性能。

闭环控制集成:将位移信号直接反馈给运动控制器,实现真正意义上的实时闭环控制。

更高精度ADC:使用12位或16位ADC提升信噪比,进一步降低量化误差。

开源与标准化:公开硬件设计与FPGA代码,促进学术与工业界的采用与改进。

LIA研究13–Magnitude and Phase Calibration of Lock-In Amplifiers, and Analysis of the Noise Response

创新点

首次实现LIA幅值与相位的同步高精度校准,覆盖100 Hz–10 kHz频率范围。

提出完整的校准链不确定度评估模型,涵盖分压器、采样表、LIA等多个环节。

系统分析LIA低通滤波器对噪声响应的影响,特别是混叠效应与滤波器阶数的关系。

使用商用设备搭建可溯源的校准系统,具备可重复性和实用性。

不足之处

频率范围有限:仅覆盖100 Hz–10 kHz,未延伸至更高频段(如MHz级别)。

温度影响未完全量化:虽在温控实验室进行,但未系统分析温度波动对校准结果的影响。

仅测试单一型号LIA:虽然测试了三台同型号设备,但结论是否适用于其他品牌或型号尚待验证。

噪声分析仅限于电阻热噪声,未考虑其他噪声源或实际信号中的谐波干扰。

后续可改进方向

扩展频率范围:向上延伸至100 kHz或MHz频段,覆盖更多LIA应用场景。

多型号LIA测试:验证校准方法对其他品牌和型号LIA的适用性。

温度敏感性分析:系统研究温度变化对校准结果的影响,建立温度补偿模型。

实际信号校准:引入含谐波、调制或非平稳特性的信号,验证校準方法的鲁棒性。

自动化校准系统:开发软件控制平台,实现全自动、多参数、快速校准。

不确定度进一步压缩:优化分压器设计(如使用约瑟夫森电压标准),降低主导不确定度来源。

这篇文章的方法虽然不能全套实现在单块FPGA上,但它为如何通过外部基准系统来校准一个FPGA-based LIA,并最终将校准结果内嵌到FPGA固件中实现实时补偿,提供了一套完整、可靠、可溯源的方案。

原始微弱信号(如温度变化、振动、生物电)→ 用高频 / 中频载波 “调制”(得到调幅 / 调相信号)→ 交流放大(避免直流漂移)→ 混频解调(提取与调制信号同步的成分)→ 低通滤波(滤除解调后的高频残余)→ 输出 “与原始调制信号一致的信号”。

LIA 输出不一定是直流:输出波形与 “原始调制信号” 完全一致 —— 调制信号是直流 / 缓慢变,输出接近直流;调制信号是交变,输出是对应的交变信号。“微弱信号检测” 的核心是 “还原信号”:幅度是信号的重要参数,但不是全部;LIA 的目标是从噪声中 “提取原始信号的完整特征(波形、幅度、相位)”,比如脑电的波形、振动的周期,这些都需要 “还原信号” 才能获得。高频 / 低频小信号都需要交流放大:无论是高频还是低频小信号,只要被调制到交流载波上,都需要先交流放大 —— 目的是提升信号幅度、避开直流漂移,否则解调后信噪比过低,无法还原原始信号。

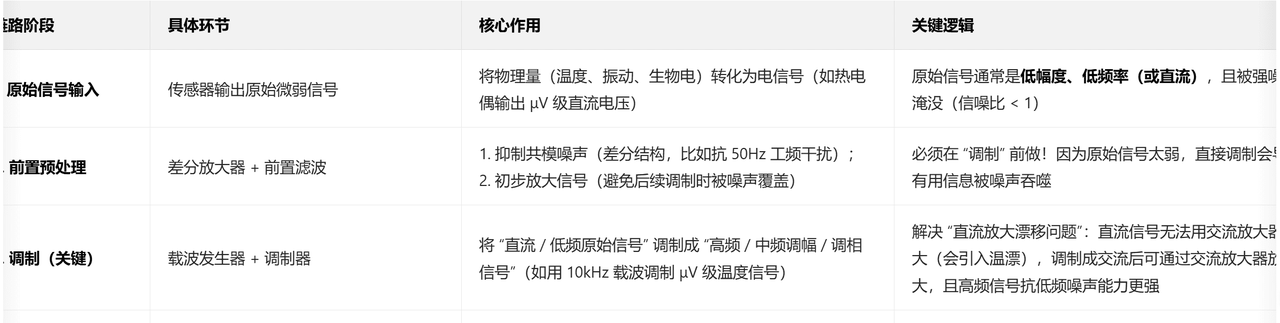

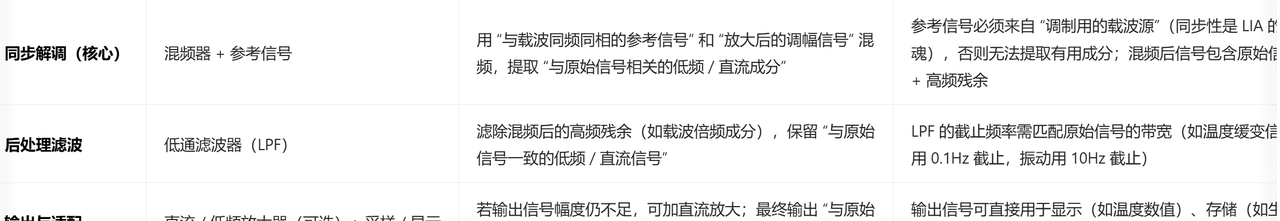

一、LIA 通用完整链路(底层逻辑不变)

无论原始信号是直流缓变、低频交变还是高频微弱,LIA 的核心是 “用同步参考信号锁定有用成分”,完整链路需包含 “信号输入 – 前置处理 – 调制 – 放大 – 同步解调 – 后处理 – 输出” 7 大模块,每个环节的作用和顺序都有明确目的:

二、按 “原始微弱信号类型” 分类的完整链路

LIA 的链路差异主要体现在 “是否需要额外调制” 和 “参考信号来源”—— 高频原始信号本身就是交流,可跳过 “外部调制”;直流 / 低频原始信号必须调制。以下分 3 类场景,对应你提到的温度、振动、生物电:

类别 1:原始信号为 “直流 / 缓变信号”(如温度、缓慢位移)

核心问题:原始信号接近直流,无法直接用交流放大器放大(会引入直流漂移),必须先调制。

完整链路:

温度传感器(输出 μV 级直流信号)→ 差分前置放大器(抑制共模噪声,放大到 nV 级)→ 带通滤波(滤除低频噪声)→ 10kHz 载波调制器(调幅:载波幅度随温度变化) → 高增益交流放大器(放大到 mV 级,抑制直流漂移)→ 混频器(输入:放大后的调幅信号 + 与载波同频同相的参考信号) → 低通滤波(截止 0.1Hz,滤除 10kHz 残余)→ 直流放大器(可选,放大到 V 级)→ 输出(与温度变化一致的直流信号,可显示温度值)。

例子:用 LIA 测热电偶的微弱温度信号(环境噪声 50Hz 干扰强):

原始信号:0.1℃温度变化对应 10μV 直流电压,被 50Hz(mV 级)噪声淹没;调制后:10kHz 载波的幅度随 10μV 直流变化(调幅信号);解调后:滤除 10kHz 和 50Hz 噪声,输出与 0.1℃变化一致的直流信号,信噪比提升 1000 倍。

类别 2:原始信号为 “低频交变信号”(如机械振动、生物电)

核心问题:原始信号是低频交流(如 10Hz 振动、1Hz 脑电),虽无需调制为高频,但需 “同步解调” 提取与参考信号同频的成分(抑制其他频率噪声)。

完整链路:

振动传感器(输出 10Hz、μV 级交变信号)→ 差分前置放大器(抑制共模噪声,放大到 nV 级)→ 带通滤波(10Hz±1Hz,滤除其他频率噪声)→ (无需额外调制,直接用 10Hz 参考信号同步) 高增益交流放大器(放大到 mV 级,避开直流漂移)→ 混频器(输入:放大后的 10Hz 信号 + 10Hz 同步参考信号) → 低通滤波(截止 20Hz,滤除混频后的高频残余)→ 低频放大器(可选,放大到 V 级)→ 输出(与振动一致的 10Hz 交变信号,可观察振动波形)。

例子:用 LIA 测电机的微弱振动(背景有 200Hz 电磁噪声):

原始信号:电机 10Hz 振动对应 5μV 交变电压,被 200Hz(100μV)噪声淹没;参考信号:取自电机的转速同步信号(10Hz,与振动同频);解调后:仅提取 10Hz 成分,滤除 200Hz 噪声,输出 10Hz 的振动波形,幅度反映振动强度。

类别 3:原始信号为 “高频微弱信号”(如射频小信号、激光干涉信号)

核心问题:原始信号是高频交流(如 1MHz 射频、100kHz 激光信号),本身已是交流,无需 “外部调制”,但需 “同步混频” 将其降频(便于后续低通滤波)。

完整链路:

射频传感器(输出 1MHz、nV 级高频信号)→ 差分前置放大器(高频低噪声放大,到 μV 级)→ 带通滤波(1MHz±10kHz,滤除其他频段噪声)→ (无需额外调制,直接用 1MHz 参考信号) 高增益高频放大器(放大到 mV 级)→ 混频器(输入:1MHz 信号 + 1MHz 同步参考信号,混频后产生直流 / 低频成分) → 低通滤波(截止 1kHz,滤除高频残余)→ 直流放大器(可选)→ 输出(与原始 1MHz 信号幅度 / 相位一致的直流 / 低频信号,可测量射频信号强度)。

例子:用 LIA 测微弱激光干涉信号(100kHz,被背景光噪声淹没):

原始信号:激光干涉产生 100kHz、1μV 高频信号,背景光噪声达 100μV;参考信号:取自激光的调制源(100kHz,与干涉信号同频);解调后:混频降频为直流信号,滤除背景噪声,输出直流幅度反映激光干涉强度。

三、总结:LIA 链路的核心不变与差异

核心不变:

始终围绕 “同步检测”—— 通过 “调制(将有用信号转化为可放大的交流)” 和 “解调(用同步参考信号锁定有用成分)”,抑制与参考信号不同频的噪声,最终输出 “与原始微弱信号一致的信号”(不是只看幅度,而是还原波形 / 变化趋势)。

链路差异:

直流 / 缓变信号:必须加 “高频载波调制”,否则无法避开直流漂移;低频交变信号:无需额外调制,但需 “与信号同频的参考信号” 同步;高频微弱信号:无需调制,直接用 “与信号同频的参考信号” 混频降频,便于滤波。

相关文章