把算力榨干:CMSIS-NN 加速路径(卷积/FC/激活的可验证替换法)

关键词

CMSIS-NN、Cortex-M、int8 量化、per-channel、TensorFlow Lite Micro、arm_convolve_s8、arm_depthwise_conv_s8、arm_fully_connected_s8、池化、DWT 计时、端到端 FPS

摘要

同一颗 Cortex-M,在不改模型结构的前提下,仅替换内核即可获得 1.5×–5× 的层级提速。关键在三点:量化口径统一(权重 per-channel、激活 per-tensor)、选择正确的 CMSIS-NN API(卷积/深度卷积/FC/池化/逐元素)以及可重复的测量与对比(DWT 周期计时、层级 MSE/余弦相似度、整网 FPS)。本文按“基线→逐层替换→验证”的顺序给出可直接粘贴的参数映射与调用骨架,并列出常见坑:尺度/零点不一致、padding/stride 口径不符、scratch 配置不足导致的隐性回退。

目录

加速前的地基:量化口径与数据布局

1.1 NHWC 与 int8 路径:激活 per-tensor、权重 per-channel 的约定

1.2 scale/zero_point、multiplier/shift 的来源与校验

1.3 参考输出与容差:dequant→float 的对齐标准(MSE/余弦相似度)

替换清单与映射关系

2.1 Conv2D →

arm_convolve_s8

2.2 Depthwise →

arm_depthwise_conv_s8

2.3 全连接 →

arm_fully_connected_s8

2.4 池化/逐元素 →

arm_avgpool_s8

arm_max_pool_s8

arm_add_s8

arm_mul_s8

2.5 ReLU/Relu6:用 activation_min/max 完成裁剪(无需额外 softmax/激活算子)

参数与缓冲:per-channel 量化、scratch 与对齐

3.1

cmsis_nn_conv_params

cmsis_nn_per_channel_quant_params

3.2 scratch 统一静态分配:

*_get_buffer_size()

3.3 权重/偏置/激活的 16–64B 对齐与放置(DTCM/SRAM/AXI)

调用骨架:把一层先替换跑通

4.1 输入/输出张量视图(NHWC int8)

4.2 单层计时:DWT CYCCNT 微基准

4.3 数值对齐:与参考实现逐层比对(阈值化前的 logits)

整网替换与回退策略

5.1 逐层切换开关:Conv/Depthwise/FC 优先

5.2 不可替换层的保底路径与分支管理

5.3 Winograd/im2col 的取舍与“峰值内存↔速度”的权衡

验证闭环:层级延迟与整体 FPS

6.1 p50/p95/p99(层级与端到端)的记录口径

6.2 漂移监测:量化不一致导致的精度偏移判据

6.3 回归模板:基线 vs CMSIS-NN 的 CSV 字段

平台细节与编译选项

7.1 M4/M7/DSP 扩展与编译开关(

-O3 -mthumb -mcpu=... -DARM_MATH_DSP

7.2 Cache/DMA 与非缓存区:M7 的一致性处理

7.3 FreeRTOS 下的任务优先级与双缓冲

常见坑与排错清单

8.1 per-channel 乘子/移位与通道错位

8.2 pad/stride 口径与有效感受野不一致

8.3 scratch 不足导致的隐性性能回退

8.4 输入零点/输出 clamp 范围错误引发饱和与梯度丢失(推理阶段的等效问题)

1. 加速前的地基:量化口径与数据布局

1.1 数据布局与定点约定

布局:TFLM 与 CMSIS-NN 都按 NHWC(

[N,H,W,C]

[out_c,k_h,k_w,in_c]

[in_c,k_h,k_w,channel_mult]

量化口径(推荐)

激活:

int8

scale_a

zero_point_a

int8

scale_w[c]

int32

bias

q

=

bias

fp

/

(

s

c

a

l

e

a

⋅

s

c

a

l

e

w

[

c

]

)

ext{bias}_q = ext{bias}_ ext{fp} / (scale_a cdot scale_w[c])

biasq=biasfp/(scalea⋅scalew[c]) 量化。

重量化(requant)关系

对每个输出通道

c

c

c:

其中

M

c

M_c

Mc、

s

c

s_c

sc 是 per-channel 乘子/移位,满足

M

c

2

31

−

s

c

≈

s

c

a

l

e

a

⋅

s

c

a

l

e

w

[

c

]

s

c

a

l

e

o

u

t

displaystyle frac{M_c}{2^{31-s_c}} approx frac{scale_acdot scale_w[c]}{scale_{out}}

231−scMc≈scaleoutscalea⋅scalew[c]。

1.2 从 TFLM 量化参数生成 CMSIS-NN 乘子/移位

// 由 TFLM 的 scale_a, scale_w[c], scale_out 计算 CMSIS-NN 的 per-channel 乘子/移位

static inline void make_requant_params(const float scale_in,

const float* scale_w, int out_ch,

const float scale_out,

int32_t* mult, int32_t* shift){

for (int c = 0; c < out_ch; ++c){

const double s = (double)scale_in * (double)scale_w[c] / (double)scale_out;

// 等同 TFLM 的 QuantizeMultiplierSmallerThanOneExp

int exp; const double q = frexp(s, &exp); // s = q * 2^exp, 0.5<=q<1

int64_t m = (int64_t)llround(q * (1ll<<31)); // 31-bit multiplier

mult[c] = (int32_t)m;

shift[c] = (int32_t)exp; // 正值表示左移(CMSIS-NN内部会按约定使用)

}

}

验证方法:随便抽几层,把 参考实现输出 dequant 成浮点,与 CMSIS-NN 输出 dequant 后做 MSE/余弦相似度;二者应在量化误差范围内一致。

1.3 激活裁剪与零点口径

ReLU/Relu6 不需要单独内核,直接用算子参数中的

activation_min/max

ReLU:

[0, 127]

zero_point_out

scale_out

activation_max

输入/输出的

zero_point

数值自检:启动时打印

in/out (scale, zp)

2. 替换清单与映射关系

2.1 Conv2D →

arm_convolve_s8

arm_convolve_s8

映射表

| 项 | TFLM/Tensor | CMSIS-NN |

|---|---|---|

| 输入激活 | |

|

| 权重 | |

|

| 偏置 | |

|

| 步幅/填充 | |

|

| 激活裁剪 | |

|

| 乘子/移位 | |

|

调用骨架(dilation=1,常见路径)

#include "arm_nnfunctions.h"

cmsis_nn_context ctx = { .buf = s_scratch, .size = scratch_bytes }; // 统一静态 scratch

cmsis_nn_conv_params p = {0};

p.padding.h = pad_h; p.padding.w = pad_w;

p.stride.h = stride_h; p.stride.w = stride_w;

p.dilation.h = 1; p.dilation.w = 1;

p.input_offset = -in_zp; // 注意号:CMSIS-NN 用负的输入零点

p.output_offset = out_zp;

p.activation.min = act_min; // 已在 int8 域

p.activation.max = act_max;

cmsis_nn_per_channel_quant_params q = { .multiplier = mult, .shift = shift };

cmsis_nn_dims in_dims = { .n = 1, .h = in_h, .w = in_w, .c = in_c };

cmsis_nn_dims filter_dims = { .n = out_c, .h = k_h, .w = k_w, .c = in_c };

cmsis_nn_dims bias_dims = { .n = 1, .h = 1, .w = 1, .c = out_c };

cmsis_nn_dims out_dims = { .n = 1, .h = out_h, .w = out_w, .c = out_c };

arm_status s = arm_convolve_s8(&ctx, &p, &q, &in_dims, in_data,

&filter_dims, w_data, &bias_dims, bias_data,

&out_dims, out_data);

注意

dilation:多数嵌入式模型取

1

input_offset

(

x

−

z

p

i

n

)

(x – zp_{in})

(x−zpin)。

2.2 DepthwiseConv2D →

arm_depthwise_conv_s8

arm_depthwise_conv_s8

通道乘子

channel_multiplier

out_c = in_c * channel_multiplier

k_h × k_w

3×3

5×5

调用骨架

cmsis_nn_dw_conv_params p = {0};

p.padding.h = pad_h; p.padding.w = pad_w;

p.stride.h = stride_h; p.stride.w = stride_w;

p.dilation.h = 1; p.dilation.w = 1;

p.ch_mult = ch_mult;

p.input_offset = -in_zp;

p.output_offset = out_zp;

p.activation.min = act_min;

p.activation.max = act_max;

cmsis_nn_per_channel_quant_params q = { .multiplier = mult, .shift = shift };

arm_status s = arm_depthwise_conv_s8(&ctx, &p, &q,

&in_dims, in_data,

&filter_dims, w_data,

&bias_dims, bias_data,

&out_dims, out_data);

2.3 FullyConnected →

arm_fully_connected_s8

arm_fully_connected_s8

确保输入被展平到

[1, 1, 1, in_features]

[out_features, in_features]

cmsis_nn_fc_params p = {0};

p.input_offset = -in_zp;

p.output_offset = out_zp;

p.filter_offset = 0; // 权重零点通常为 0(对称)

p.activation.min = act_min;

p.activation.max = act_max;

cmsis_nn_per_tensor_quant_params q = { .multiplier = mult0, .shift = shift0 }; // FC 常见 per-tensor

cmsis_nn_dims in_dims = { .n=1,.h=1,.w=1,.c=in_features };

cmsis_nn_dims w_dims = { .n=out_features,.h=1,.w=1,.c=in_features };

cmsis_nn_dims out_dims = { .n=1,.h=1,.w=1,.c=out_features };

arm_status s = arm_fully_connected_s8(&ctx, &p, &q,

&in_dims, in_data,

&w_dims, w_data,

&bias_dims, bias_data,

&out_dims, out_data);

2.4 池化与逐元素

平均池化:

arm_avgpool_s8

arm_max_pool_s8

arm_elementwise_add_s8

arm_elementwise_mul_s8

arm_relu_s8

Padding 计算(SAME/VALID)

static inline void calc_pad_same(int in, int k, int s, int* pad){

const int out = (in + s - 1) / s;

const int pad_all = ((out - 1) * s + k - in);

pad[0] = pad_all / 2; pad[1] = pad_all - pad[0]; // (head, tail)

}

3. 参数与缓冲:per-channel、scratch 与对齐

3.1 组装

cmsis_nn_*_params

cmsis_nn_*_params

Conv/Depthwise:都需要

input_offset = -zp_in

output_offset = zp_out

activation.min/max

multiplier[]/shift[]

out_c

FC:常见为 per-tensor 量化(也支持 per-channel 视版本)。

从 TFLM 张量取参数

const int zp_in = input->params.zero_point;

const float sc_in = input->params.scale;

const int zp_out = output->params.zero_point;

const float sc_out = output->params.scale;

// 权重 per-channel scale 来自 FlatBuffer 的 affine_quantization

3.2 统一静态 scratch(一次分配,多层复用)

int32_t scratch_need = 0;

scratch_need = MAX(scratch_need, arm_convolve_s8_get_buffer_size(&in_dims, &filter_dims));

scratch_need = MAX(scratch_need, arm_depthwise_conv_s8_get_buffer_size(&in_dims, &filter_dims));

static uint8_t ALIGN(16) s_scratch[SCRATCH_MAX]; // 放 DTCM/SRAM,避免片外抖动

cmsis_nn_context ctx = { .buf = s_scratch, .size = SCRATCH_MAX };

不同版本

的签名可能带

*_get_buffer_size(),以你使用的头文件为准;统一在初始化阶段聚合最大需求,推理时不再分配。

out_dims/stride/pad

3.3 对齐与放置(总线/Cache 友好)

权重/偏置对齐到 16–64B;激活/临时缓冲同样对齐,利于突发与 cacheline 对齐。

放置建议

DTCM/SRAM:激活、scratch、环形 I/O 缓冲;AXI SRAM:大 tile/搬运中转;Flash/PSRAM:权重常驻,按层搬运到 SRAM 使用。

段属性示例(GCC)

#define ALIGN(N) __attribute__((aligned(N)))

__attribute__((section(".dtcm_bss"))) ALIGN(64) int8_t act0[ACT_MAX], act1[ACT_MAX];

__attribute__((section(".dtcm_bss"))) ALIGN(64) uint8_t s_scratch[SCRATCH_MAX];

__attribute__((section(".axi_bss"))) ALIGN(64) int8_t w_tile[TILE_MAX];

3.4 单层可复用计时器(DWT)

static inline void dwt_init(void){

CoreDebug->DEMCR |= CoreDebug_DEMCR_TRCENA_Msk;

DWT->CYCCNT = 0u; DWT->CTRL |= DWT_CTRL_CYCCNTENA_Msk;

}

static inline uint32_t dwt_us(void){

return DWT->CYCCNT / (SystemCoreClock/1000000u);

}

用

围出 Conv/Depthwise/FC 的调用,形成 层级 p50/p95/p99,并与替换前的 TFLM 参考实现对比 提速倍数 与 数值偏差(MSE/余弦)。

dwt_us()

4. 调用骨架:先把“一层”替换跑通并对齐数值

目标:同一层卷积/深度卷积/FC,在同一输入与量化口径下,分别跑 参考实现(REF) 与 CMSIS-NN,量化时间与数值偏差。确认无偏移后,再推广到全网。

4.1 统一的层描述与入口

typedef struct {

// NHWC

const int8_t* in; int in_h, in_w, in_c; int in_zp; float in_sc;

// OHWI / Depthwise: IHWO

const int8_t* w; int k_h, k_w; // Conv: out_c known; DW: ch_mult

const int32_t* b; // per-channel int32 bias

// 输出

int8_t* out; int out_h, out_w, out_c; int out_zp; float out_sc;

// 超参数

int stride_h, stride_w;

int pad_h, pad_w;

int dilation_h, dilation_w; // 本文示例均设为 1

int ch_mult; // Depthwise 使用

// 量化

const float* w_sc_pc; // 权重 per-channel scale[out_c]

const int32_t* mult_pc; // CMSIS-NN requant 乘子[out_c]

const int32_t* shift_pc; // CMSIS-NN requant 移位[out_c]

// 激活裁剪(int8 域)

int act_min, act_max;

} conv_args_s8_t;

可按前文 §1.2 由

mult_pc/shift_pc生成。

{in_sc, w_sc_pc[c], out_sc}直接是 int8 范围(例如 ReLU:

act_min/max)。

0..127

4.2 参考实现(REF)与 CMSIS-NN 的双跑骨架

typedef struct { uint32_t us; float mse, cos_sim; int max_abs_diff; } layer_report_t;

// 简化:用 DWT 计时;在 host 侧可改 steady_clock

static inline uint32_t dwt_us(void){

return DWT->CYCCNT / (SystemCoreClock/1000000u);

}

// 简单的 REF:可接 TFLM reference_integer_ops::Conv;这里示意

void conv_ref_s8(const conv_args_s8_t* a, int8_t* out_ref);

// Dequant 并做误差度量

static layer_report_t eval_diff(const conv_args_s8_t* a,

const int8_t* out_ref, const int8_t* out_opt,

uint32_t t_ref_us, uint32_t t_opt_us){

const int N = a->out_h * a->out_w * a->out_c;

double sse=0, dot=0, n1=0, n2=0; int mad=0;

for (int i=0;i<N;i++){

const float yr = (out_ref[i] - a->out_zp) * a->out_sc;

const float yo = (out_opt[i] - a->out_zp) * a->out_sc;

const int di = (int)out_ref[i] - (int)out_opt[i];

sse += (yo-yr)*(yo-yr);

dot += yo*yr; n1 += yo*yo; n2 += yr*yr;

int ad = di>0?di:-di; if (ad>mad) mad=ad;

}

layer_report_t r;

r.us = t_opt_us;

r.mse = (float)(sse / (double)N);

r.cos_sim = (float)(dot / (sqrt(n1)*sqrt(n2) + 1e-12));

r.max_abs_diff = mad;

return r;

}

// —— 卷积单层双跑(Conv2D)— 以 arm_convolve_s8 为例

#include "arm_nnfunctions.h"

layer_report_t bench_conv2d_once(conv_args_s8_t* a, uint8_t* scratch, int scratch_sz){

// 1) REF 输出

// 注意:避免大栈;这里复用 out 作为 opt,额外开一块 out_ref

const int N = a->out_h * a->out_w * a->out_c;

static int8_t* out_ref; // 预分配

uint32_t t0 = dwt_us(); conv_ref_s8(a, out_ref); uint32_t t1 = dwt_us();

// 2) CMSIS-NN 调用

cmsis_nn_context ctx = { .buf = scratch, .size = scratch_sz };

cmsis_nn_conv_params p = {0};

p.padding.h=a->pad_h; p.padding.w=a->pad_w;

p.stride.h=a->stride_h; p.stride.w=a->stride_w;

p.dilation.h=1; p.dilation.w=1; // 示意:不支持扩张卷积时保持 1

p.input_offset = -a->in_zp;

p.output_offset = a->out_zp;

p.activation.min = a->act_min; p.activation.max = a->act_max;

cmsis_nn_per_channel_quant_params q = { .multiplier=(int32_t*)a->mult_pc,

.shift=(int32_t*)a->shift_pc };

cmsis_nn_dims in_dims = { .n=1,.h=a->in_h,.w=a->in_w,.c=a->in_c };

cmsis_nn_dims f_dims = { .n=a->out_c,.h=a->k_h,.w=a->k_w,.c=a->in_c };

cmsis_nn_dims b_dims = { .n=1,.h=1,.w=1,.c=a->out_c };

cmsis_nn_dims o_dims = { .n=1,.h=a->out_h,.w=a->out_w,.c=a->out_c };

uint32_t t2 = dwt_us();

arm_status s = arm_convolve_s8(&ctx, &p, &q, &in_dims, a->in,

&f_dims, a->w, &b_dims, a->b,

&o_dims, a->out);

uint32_t t3 = dwt_us();

if (s != ARM_MATH_SUCCESS) { /* 回退或报错 */ }

// 3) 度量

return eval_diff(a, out_ref, a->out, t1-t0, t3-t2);

}

合格线(建议)

数值:

max_abs_diff ≤ 2

cos_sim ≥ 0.999

MSE ≤ 1e-3

speedup = t_ref / t_opt

深度卷积 / FC 完全同理,用

、

arm_depthwise_conv_s8替换即可(参数映射见前文 §2.2/2.3)。

arm_fully_connected_s8

4.3 CSV 输出(用于回归与对比)

layer,name,type,H,W,Chi,Cho,k,sh,sw,padh,padw,t_ref_us,t_opt_us,speedup,mse,cos,max_abs

0,conv1,conv,64,64,16,16,3,1,1,1,1,420,160,2.62,0.0007,0.9996,1

...

5. 整网替换与回退策略

目标:逐层开关、可回退、可观测。任何不满足 CMSIS-NN 约束的层,自动回退到参考路径,确保功能正确优先。

5.1 逐层开关与判定

typedef enum { IMPL_REF=0, IMPL_CMSIS=1 } impl_t;

typedef struct {

impl_t conv, depthwise, fc, pool, eltwise; // 全局缺省

} accel_policy_t;

typedef struct {

int layer_id; int type; // 0 conv, 1 dw, 2 fc ...

impl_t impl_override; // 可选:逐层覆盖

} layer_meta_t;

// 判定当前层是否满足 CMSIS-NN 约束

static bool cmsis_conv_supported(const conv_args_s8_t* a){

if (a->dilation_h!=1 || a->dilation_w!=1) return false;

if (a->k_h<1 || a->k_w<1) return false;

// 某些优化核对 3x3/5x5 友好;非常规尺寸可先走通用核或回退

// 对齐/步幅约束也可在此编码

return true;

}

调度骨架(伪码)

void run_network(const accel_policy_t* pol){

for (int i=0; i<nn.num_layers; ++i){

switch (nn.layers[i].type){

case L_CONV:{

conv_args_s8_t a = build_conv_args(i);

bool ok = (pol->conv==IMPL_CMSIS) && cmsis_conv_supported(&a);

if (ok){

if (arm_convolve_s8(..., &status)==ARM_MATH_SUCCESS) break;

// 启动失败 → 回退

}

conv_ref_s8(&a, a.out); // REF 路径

} break;

case L_DW: { /* 同理调用 arm_depthwise_conv_s8 或回退 */ } break;

case L_FC: { /* arm_fully_connected_s8 或回退 */ } break;

default: { /* 其它算子保持参考实现 */ } break;

}

}

}

可观测:每层输出一行日志/CSV,写明

、耗时、是否回退与原因(不支持/启动失败)。

impl=CMSIS/REF

5.2 回退情形与处理

不支持的超参数:

dilation>1

→ 直接走 REF,并在导出端评估是否可改结构(例如把 dilated conv 改为空洞等效或近似)。算子 scratch 超过阈值:避免峰值内存失控。

→ 设阈值(如

scratch_need > SRAM * 0.3

max_abs_diff > 2

cos_sim < 0.998

→ 暂时回退,导出/量化侧重新校准 scale/零点或核对 per-channel 表。

5.3 Winograd / im2col 的取舍(速度 ↔ 峰值)

Winograd:适合

3×3 stride=1

规则:当层输出面积 ≥ 某阈值(例如

Ho×Wo×Co > 20k

im2col + GEMM:通用且简单,但 临时缓冲 = Ho×Wo×Kh×Kw×Ci(int8 字节),在 SRAM 紧张时极易爆峰。

规则:若

im2col_bytes > 0.25 × SRAM_avail

5.4 “一键切换”与 CI 守门

编译时开关:

-DNN_USE_CMSIS=1

accel_policy_t

回归守门:两套跑法(REF / CMSIS-NN)都跑一遍,产出两份 CSV;CI 比较:

p95(infer)

arena_used

示例:层级统计汇总

impl, layers_total, layers_cmsis, fallback_unsupported, fallback_scratch, fallback_drift

CMSIS, 14, 12, 1, 0, 1

5.5 端到端与任务调度的整合

双缓冲:前处理 / 推理分两个缓冲 ping-pong;推理任务高优先级,避免 p99 抖动。权重搬运与计算重叠:若权重在片外,按层预取到 SRAM(AXI DMA),与上一层计算重叠。栈/arena 余量:推理任务栈余量 ≥20%;

arena_used ≤ arena_size × 0.85

6. 验证闭环:层级延迟与整体 FPS

6.1 记录口径:层级 + 端到端两套表

层级(每个 Conv/DW/FC):

t_ref_us / t_opt_us / speedup / mse / cos / max_abs

pre_us / infer_us / post_us / L_ms / FPS

FPS 定义

单网推理吞吐(不含 I/O):

FPS_infer = 1000 / p50(infer_ms)

FPS_e2e = 1000 / p50(L_ms)

L_ms = max(W, pre+infer+post)+sched

6.2 采样骨架(环形缓冲 + CSV)

typedef struct {

uint32_t us_ref, us_opt; // 层级

float mse, cos; int8_t max_abs;

uint16_t layer_id; uint8_t type; // 0 conv,1 dw,2 fc

} lyr_row_t;

typedef struct {

uint32_t pre_us, infer_us, post_us; // 端到端

uint32_t L_ms_x100; // 以 0.01ms 计,避免浮点

} e2e_row_t;

static volatile lyr_row_t s_lyr[256];

static volatile e2e_row_t s_e2e[1024];

static volatile uint16_t s_w_lyr=0, s_w_e2e=0;

static inline void put_lyr(const lyr_row_t* r){

uint16_t i = __atomic_fetch_add(&s_w_lyr,1,__ATOMIC_RELAXED)&0xFF;

s_lyr[i] = *r;

}

static inline void put_e2e(const e2e_row_t* r){

uint16_t i = __atomic_fetch_add(&s_w_e2e,1,__ATOMIC_RELAXED)&0x3FF;

s_e2e[i] = *r;

}

导出 CSV(主机串口侧或文件系统)

layer, type, us_ref, us_opt, speedup, mse, cos, max_abs

e2e, pre_us, infer_us, post_us, L_ms

6.3 p50/p95/p99 的在线估计(常数空间)

长跑时不想保留全量数据,可用 P² 分位点估计(或固定 64 桶直方图近似):

typedef struct { double p50,p95,p99; /* 内部状态略 */ } qtracker_t;

void qt_init(qtracker_t* q); void qt_push(qtracker_t* q, double x);

在

put_e2e()

infer_us

L_ms

6.4 基线对比模板(CSV 字段)

case, p50_infer_us, p95_infer_us, p99_infer_us, p50_L_ms, p95_L_ms, p99_L_ms, arena_used, stack_low_b

门槛(示例):

p95_infer_us(CMSIS) ≤ p95_infer_us(REF)

p99_L_ms

arena_used

stack_low_b

7. 平台细节与编译选项

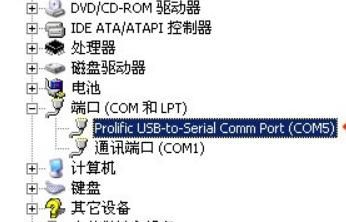

7.1 编译/链接建议(GCC/CMake)

优化与目标核

M4:

-O3 -mcpu=cortex-m4 -mthumb -DARM_MATH_DSP

-O3 -mcpu=cortex-m7 -mthumb -DARM_MATH_DSP -ffast-math

-ffunction-sections -fdata-sections -fno-exceptions -fno-rtti -fno-unwind-tables

链接去除死代码:

-Wl,--gc-sections

LTO(可选):

-flto

头文件/宏:

-DTF_LITE_STATIC_MEMORY -DTF_LITE_MCU_DEBUG_LOG

CMake 片段

set(CFLAGS "-O3 -mcpu=cortex-m7 -mthumb -DARM_MATH_DSP -ffunction-sections -fdata-sections -fno-exceptions -fno-rtti")

set(LDFLAGS "-Wl,--gc-sections")

add_compile_options(${CFLAGS})

add_link_options(${LDFLAGS})

7.2 Cache / DMA / 非缓存区(M7 常见)

启用 I/D-Cache(上电早期):

SCB_EnableICache(); SCB_EnableDCache();

DMA 读写缓冲使用非缓存区或做 Cache 维护:

static inline void cache_clean(const void* p, size_t n){ SCB_CleanDCache_by_Addr((void*)p, n); }

static inline void cache_inval(void* p, size_t n){ SCB_InvalidateDCache_by_Addr(p, n); }

// DMA 发送前 Clean,接收后 Invalidate

若可用 MPU,为 DMA 区域配置 Write-Through/Non-cacheable。

7.3 存储放置与对齐

Arena / scratch / 激活:DTCM/SRAM(对齐 16–64B)。权重:Flash/PSRAM;按层搬运到 AXI-SRAM 再计算,减少片外抖动。I/O 帧/Tile:AXI-SRAM,便于 DMA 与 CPU/NPU 重叠。

段属性示例

__attribute__((section(".dtcm_bss"), aligned(64))) uint8_t s_scratch[SCR_MAX];

__attribute__((section(".dtcm_bss"), aligned(64))) int8_t act0[ACT_MAX], act1[ACT_MAX];

__attribute__((section(".axi_bss"), aligned(64))) int8_t tile_w[TILE_MAX];

7.4 FreeRTOS 调度建议

优先级:

preproc_task > infer_task > log_task

uxTaskGetStackHighWaterMark()

8. 常见坑与排错清单

8.1 量化尺度/零点不一致

症状:输出全饱和/全 0、cos_sim 显著下降。排查:打印

in/out scale,zp

mult/shift

8.2 pad/stride 口径错位

症状:尺寸不符或边缘特征异常。排查:明确 SAME/VALID 计算;逐层打印

Ho×Wo×Co

calc_pad_same()

8.3 scratch 不足的隐性回退/退化

症状:性能未提升甚至更慢;偶发失败。排查:在初始化阶段调用

*_get_buffer_size()

8.4

im2col

im2col

症状:Arena 逼近上限、端到端 p99 飘高。修复:改 direct/Winograd;缩输入/通道;标准卷积改 DW+PW。

8.5 权重/激活未对齐或不在快 RAM

症状:提速不明显,长尾增加。修复:对齐 16–64B;激活/临时缓冲放 DTCM/SRAM;片外权重按层预取到 SRAM。

8.6 per-channel 表长度/顺序错误

症状:少量通道严重偏移。排查:遍历

out_c

mult/shift

8.7 dilation / 非常规核尺寸

症状:CMSIS-NN 返回不支持或执行错误。修复:导出端替换等效结构;或该层回退参考路径。

8.8 端到端只看

Invoke()

Invoke()

症状:单层快了,总体 FPS 不升。排查:记录

pre/infer/post/sched

8.9 Cache/DMA 不一致

症状:偶发花数据/随机错误。修复:DMA 前

Clean

Invalidate

8.10 回归守门缺失

症状:某次合入导致性能/精度回退未被发现。修复:CI 比对 CSV:

p95/99(infer/L)

arena_used

max_abs_diff

个人简介

作者简介:全栈研发,具备端到端系统落地能力,专注人工智能领域。

个人主页:观熵

个人邮箱:privatexxxx@163.com

座右铭:愿科技之光,不止照亮智能,也照亮人心!

专栏导航

观熵系列专栏导航:

具身智能:具身智能

国产 NPU × Android 推理优化:本专栏系统解析 Android 平台国产 AI 芯片实战路径,涵盖 NPU×NNAPI 接入、异构调度、模型缓存、推理精度、动态加载与多模型并发等关键技术,聚焦工程可落地的推理优化策略,适用于边缘 AI 开发者与系统架构师。

DeepSeek国内各行业私有化部署系列:国产大模型私有化部署解决方案

智能终端Ai探索与创新实践:深入探索 智能终端系统的硬件生态和前沿 AI 能力的深度融合!本专栏聚焦 Transformer、大模型、多模态等最新 AI 技术在 智能终端的应用,结合丰富的实战案例和性能优化策略,助力 智能终端开发者掌握国产旗舰 AI 引擎的核心技术,解锁创新应用场景。

企业级 SaaS 架构与工程实战全流程:系统性掌握从零构建、架构演进、业务模型、部署运维、安全治理到产品商业化的全流程实战能力

GitHub开源项目实战:分享GitHub上优秀开源项目,探讨实战应用与优化策略。

大模型高阶优化技术专题

AI前沿探索:从大模型进化、多模态交互、AIGC内容生成,到AI在行业中的落地应用,我们将深入剖析最前沿的AI技术,分享实用的开发经验,并探讨AI未来的发展趋势

AI开源框架实战:面向 AI 工程师的大模型框架实战指南,覆盖训练、推理、部署与评估的全链路最佳实践

计算机视觉:聚焦计算机视觉前沿技术,涵盖图像识别、目标检测、自动驾驶、医疗影像等领域的最新进展和应用案例

国产大模型部署实战:持续更新的国产开源大模型部署实战教程,覆盖从 模型选型 → 环境配置 → 本地推理 → API封装 → 高性能部署 → 多模型管理 的完整全流程

Agentic AI架构实战全流程:一站式掌握 Agentic AI 架构构建核心路径:从协议到调度,从推理到执行,完整复刻企业级多智能体系统落地方案!

云原生应用托管与大模型融合实战指南

智能数据挖掘工程实践

Kubernetes × AI工程实战

TensorFlow 全栈实战:从建模到部署:覆盖模型构建、训练优化、跨平台部署与工程交付,帮助开发者掌握从原型到上线的完整 AI 开发流程

PyTorch 全栈实战专栏: PyTorch 框架的全栈实战应用,涵盖从模型训练、优化、部署到维护的完整流程

深入理解 TensorRT:深入解析 TensorRT 的核心机制与部署实践,助力构建高性能 AI 推理系统

Megatron-LM 实战笔记:聚焦于 Megatron-LM 框架的实战应用,涵盖从预训练、微调到部署的全流程

AI Agent:系统学习并亲手构建一个完整的 AI Agent 系统,从基础理论、算法实战、框架应用,到私有部署、多端集成

DeepSeek 实战与解析:聚焦 DeepSeek 系列模型原理解析与实战应用,涵盖部署、推理、微调与多场景集成,助你高效上手国产大模型

端侧大模型:聚焦大模型在移动设备上的部署与优化,探索端侧智能的实现路径

行业大模型 · 数据全流程指南:大模型预训练数据的设计、采集、清洗与合规治理,聚焦行业场景,从需求定义到数据闭环,帮助您构建专属的智能数据基座

机器人研发全栈进阶指南:从ROS到AI智能控制:机器人系统架构、感知建图、路径规划、控制系统、AI智能决策、系统集成等核心能力模块

人工智能下的网络安全:通过实战案例和系统化方法,帮助开发者和安全工程师识别风险、构建防御机制,确保 AI 系统的稳定与安全

智能 DevOps 工厂:AI 驱动的持续交付实践:构建以 AI 为核心的智能 DevOps 平台,涵盖从 CI/CD 流水线、AIOps、MLOps 到 DevSecOps 的全流程实践。

C++学习笔记?:聚焦于现代 C++ 编程的核心概念与实践,涵盖 STL 源码剖析、内存管理、模板元编程等关键技术

AI × Quant 系统化落地实战:从数据、策略到实盘,打造全栈智能量化交易系统

大模型运营专家的Prompt修炼之路:本专栏聚焦开发 / 测试人员的实际转型路径,基于 OpenAI、DeepSeek、抖音等真实资料,拆解 从入门到专业落地的关键主题,涵盖 Prompt 编写范式、结构输出控制、模型行为评估、系统接入与 DevOps 管理。每一篇都不讲概念空话,只做实战经验沉淀,让你一步步成为真正的模型运营专家。

🌟 如果本文对你有帮助,欢迎三连支持!

👍 点个赞,给我一些反馈动力

⭐ 收藏起来,方便之后复习查阅

🔔 关注我,后续还有更多实战内容持续更新

相关文章