第二章:AI底层硬件架构:算力的基石

学习目标

掌握AI计算硬件的分类、原理及适用场景,理解不同硬件在AI全流程中的协同作用。

2.1 CPU在AI计算中的角色与局限性

角色定位:

系统控制中枢:CPU是AI服务器的“大脑”,负责操作系统指令调度、内存管理、数据流控制及I/O操作。例如,在AI加速服务器中,每8个GPU需搭配2个高端CPU以维持系统稳定运行。通用计算核心:CPU擅长处理序列化任务、复杂逻辑运算及通用应用程序。在AI全流程中,CPU贯穿数据采集、预处理、训练、推理及应用等环节。例如,在蛋白质折叠预测(AlphaFold2)中,英特尔至强可扩展处理器通过优化端到端通量能力,提供比GPU更具性价比的加速方案。异构架构协调者:在CPU+GPU/FPGA/TPU等异构架构中,CPU作为控制节点,管理加速器计算任务,实现资源高效分配。例如,腾讯云VectorDB与英特尔合作,通过第五代至强平台优化,向量检索效率提升约2.3倍。

局限性:

并行计算能力不足:CPU核心数较少(通常2-64核),主频虽高(3-5GHz),但并行计算单元有限,难以高效处理深度学习中的大规模矩阵运算。例如,训练ResNet模型时,CPU的GFLOPS吞吐量仅为GPU的几十分之一。功耗与成本限制:高端CPU功耗较高(如至强可扩展处理器TDP可达270W),且在大规模并行计算场景中,成本效益低于GPU或专用芯片。

适用场景:

轻量化推理任务(如小型传感器数据分类);AI全流程中的数据预处理、模型优化及系统维护;边缘设备中低功耗、低延迟的AI推理(如智能音箱语音交互)。

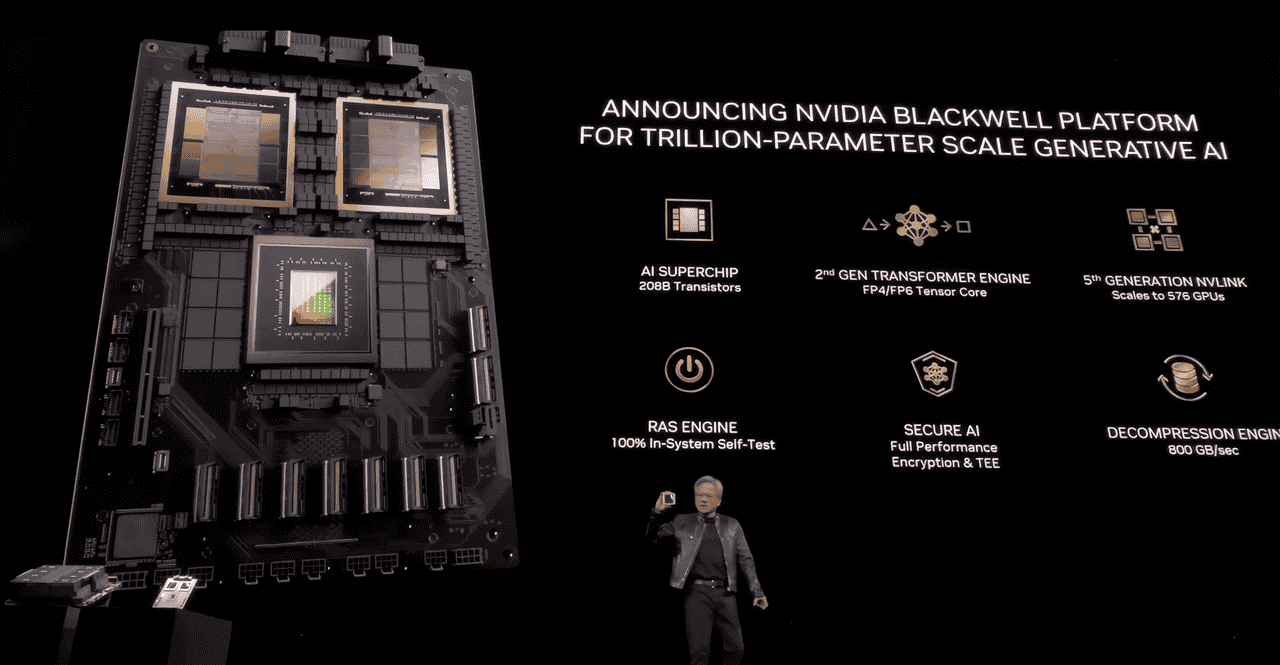

2.2 GPU架构解析:为何成为深度学习首选

架构特点:

海量并行计算单元:GPU拥有成千上万个小型计算核心(如NVIDIA RTX 3090搭载10496个CUDA核心),可同时处理数千个独立任务,完美适配深度学习中的矩阵乘法、卷积运算等高度并行操作。高带宽内存(HBM)支持:GPU通过高速显存(如GDDR6X)解决大规模数据吞吐的带宽问题,避免“数据等待”导致的算力浪费。例如,RTX 3090的AI算力达35.6 TFLOPS,而RTX 50系列通过Tensor Cores支持FP8混合精度计算,算力密度进一步提升。专用硬件加速单元:现代GPU集成Tensor Cores(如NVIDIA Volta架构)等专用单元,加速矩阵乘法等深度学习计算,显著提升训练速度。

优势:

算力强大:GPU每秒可执行数十亿次浮点运算(TFLOPS),远超CPU。例如,使用NVIDIA A100 GPU训练图像分类模型,可将百万级样本的训练时间从“天”级压缩至“小时”级。生态成熟:CUDA生态成为AI开发的事实标准,支持TensorFlow、PyTorch等主流框架,工具链丰富,开发者易上手。

局限性:

单线程任务效率低:在文档编辑、网页加载等单线程任务中,GPU效率远低于CPU。编程门槛较高:GPU编程需针对并行架构优化,存在一定技术门槛。

适用场景:

中大型深度学习模型训练(如CNN、RNN、Transformers);图形渲染与AI计算融合场景(如游戏中的光线追踪技术);科学计算与AI交叉领域(如AI for Science)。

2.3 专用AI芯片:TPU、NPU、FPGA的技术特点

TPU(张量处理单元):

架构特点:Google专为机器学习任务研发的ASIC芯片,内置大量矩阵乘法单元(MXU),直接硬件级支持张量运算,采用8位整数精度(INT8)计算,提升算力密度。例如,Ironwood TPU v7通过3D堆叠内存与高速互联技术,单机算力突破4614 TFLOPS。优势:超高AI能效比,同等算力下功耗仅为GPU的1/3-1/5。例如,训练千亿参数语言模型(如GPT-3级)时,TPU v7集群较GPU集群减少40%能耗,缩短20%训练时间。局限性:专用性强,生态锁定Google Cloud,灵活性差。适用场景:Google Cloud云端的大规模AI训练与推理(如BERT、GPT-2等模型)。

NPU(神经网络处理器):

架构特点:通常集成在SoC中作为协处理器,专注于加速AI模型推理(有时包括训练),优化卷积、池化、激活函数等操作。例如,华为昇腾、苹果A/M系列芯片中的NPU。优势:高能效、低延迟,适合电池供电设备。例如,移动设备中的面部解锁、语音助手等本地AI功能。局限性:算力有限,仅支持推理,不适合大规模模型训练;不同厂商架构差异大,生态兼容性有待提升。适用场景:移动设备(如智能手机、摄像头)、汽车电子(如自动驾驶座舱的驾驶员疲劳监测)。

FPGA(现场可编程门阵列):

架构特点:由大量可编程逻辑单元和连线资源组成,用户可通过硬件描述语言(HDL)定制电路功能,适应算法变化。优势:灵活性高,能效优于GPU,极低延迟(硬件直连处理)。例如,通信基站、金融高频交易等场景。局限性:开发难度大(需硬件工程师使用HDL开发,周期长、成本高),绝对算力通常低于顶级GPU/ASIC。适用场景:算法未定型、需要快速迭代或低延迟的推理加速场景。

2.4 边缘计算芯片:端侧AI的硬件解决方案

技术特点:

低功耗设计:边缘计算芯片(如NPU、专用AI加速器)采用低功耗架构和节能技术,延长设备电池续航时间。例如,智能手表中的健康监测功能依赖低功耗AI芯片实现实时数据处理。本地化推理:数据在本地设备处理,无需上传云端,响应快且保护隐私。例如,自动驾驶汽车通过边缘计算芯片实现实时环境感知与决策。集成化趋势:AI芯片与传感器、通信模块等集成,形成SoC解决方案,降低系统复杂度。例如,高通骁龙平台集成NPU,支持智能手机上的AI拍照优化。

适用场景:

智能家居(如智能音箱、摄像头);工业物联网(如设备预测性维护);自动驾驶(如座舱域控制器);医疗健康(如可穿戴设备健康监测)。

2.5 内存与存储:高带宽内存(HBM)与新型存储技术

HBM(高带宽内存):

技术原理:基于3D堆栈工艺,通过硅通孔(TSV)垂直堆叠多个DRAM芯片,形成大容量内存阵列,显著提升带宽并降低单位数据能耗。例如,三星12层HBM3E数据传输速度超过每秒10千兆位元。市场格局:SK海力士、三星、美光占据全球HBM市场主要份额(2025年Q2分别为62%、17%、21%)。SK海力士于2025年3月出货全球首款12层HBM4样品,计划2026年下半年量产。AI应用:HBM通过高带宽支持大规模并行计算,成为AI服务器GPU的核心组件。例如,OpenAI每月采购90万片HBM晶圆用于“星际之门”数据中心建设。

新型存储技术:

SOCAMM(压缩连接内存模块):采用LPDRAM+CAMM组合架构,通过革新性物理结构降低三分之一功耗,支持下一代LPDDR6标准,作为HBM的补充方案,已形成三星(50%)、SK海力士(30-35%)、美光(剩余)的供应格局。HAMR(热辅助磁记录)技术:应用于HDD(机械硬盘),单盘容量突破30TB,数据存储密度显著提升,成本大幅下降,成为AI数据长期沉淀的关键技术。例如,希捷通过HAMR技术满足AI训练数据、推理生成内容等长期存储需求。

相关文章