刻蚀工艺简介

刻蚀作为关键步骤,在半导体制造中扮演着不可或缺的一环。在硅片表面形成光刻胶图形后,刻蚀工艺将该图形转移到光刻胶下面的层。常见的刻蚀方法有物理性刻蚀、化学性刻蚀。而化学刻蚀由于其具备高均匀性、高选择比等优势,在半导体制造中占据主导地位。其中干法刻蚀更是占据了90%的市场份额。本文将会系统阐述硅(Si)的干法刻蚀工艺,并深入探讨刻蚀过程中一些常见的技巧与关键点。

1、刻蚀设备介绍

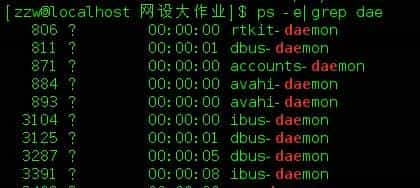

在刻蚀工艺中,针对不同的工艺需求,需要选择合适的刻蚀机台,常见的干法刻蚀设备有反应离子刻蚀(RIE)设备、感应耦合等离子体(ICP)刻蚀设备、等离子体增强化学气相沉积(PECVD)刻蚀设备等[3]。下面就这些常见的刻蚀设备以及各自的特点进行简要的叙述。

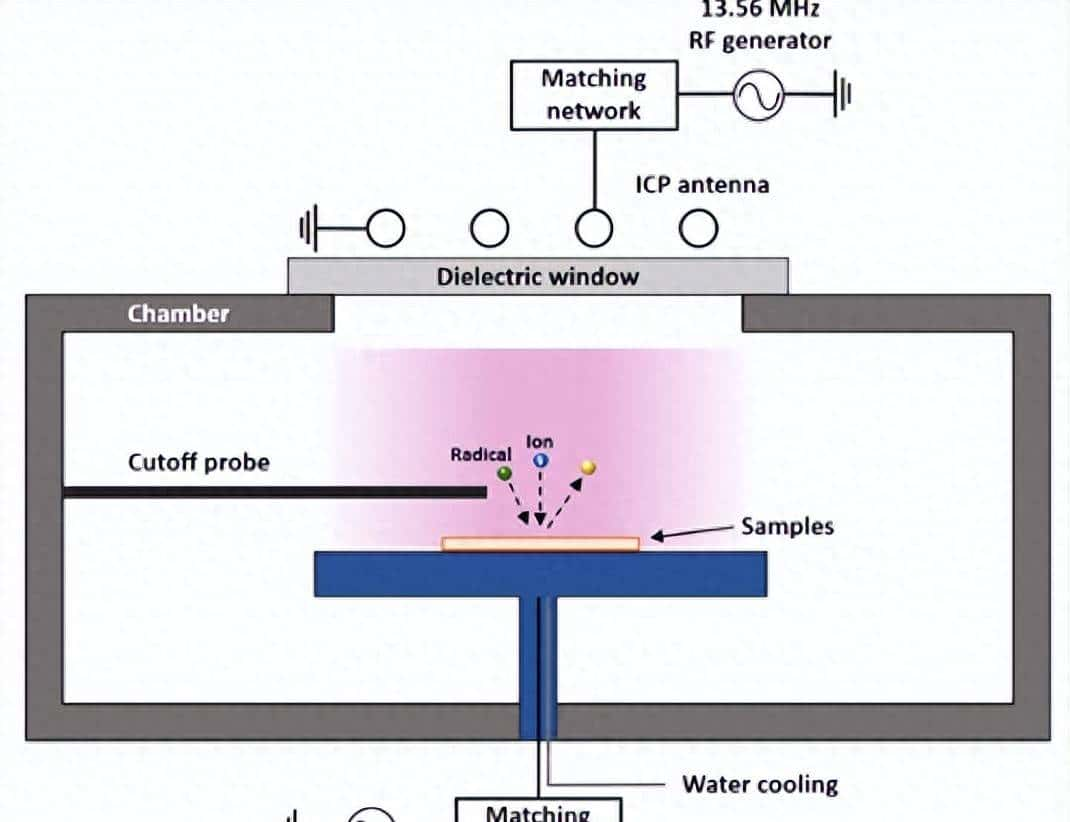

(1)反应离子刻蚀(RIE)设备

反应离子刻蚀(RIE)的机制与等离子体刻蚀技术超级类似。为了增加刻蚀方向性,采用较低的压力。一般在10-100毫托的压力下,在非对称平行板反应器中进行,并且高度各向异性,这意味着垂直刻蚀速率远高于横向刻蚀速率。持有晶圆的平面电极面积比另一个电极小得多。反应离子刻蚀的缺点是传导加热,通过将晶圆放在冷却台上限制刻蚀过程中温度升高来减少这一问题。

图1 RIE刻蚀原理[4]

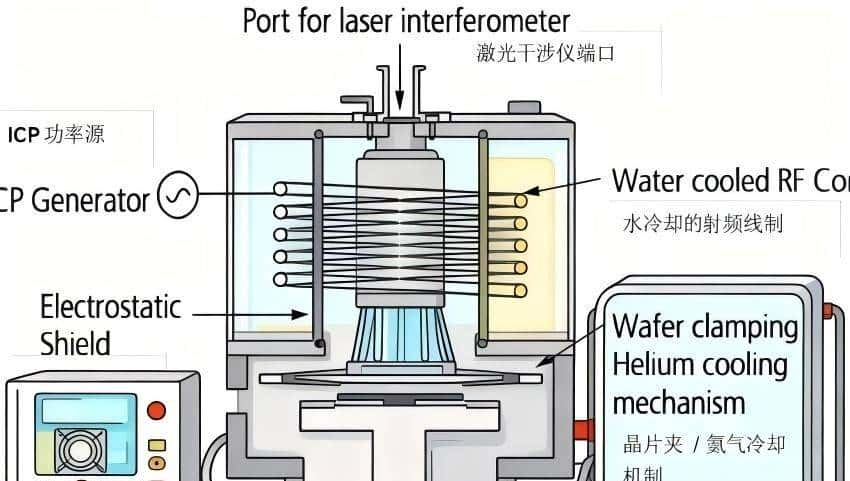

(2)感应耦合等离子体(ICP)刻蚀设备

ICP由于采用感应耦合的方式产生高密度等离子体。它有一个感应线圈,当高频电流通过线圈时,在线圈周围产生交变磁场,这个磁场会在反应腔内感应出高密度的等离子体。与RIE相比,ICP刻蚀设备能够产生更高的离子密度,从而实现更高的刻蚀速率,以及更好的选择比。适用于对刻蚀速率要求较高的场合,如高深宽比的深硅刻蚀。

图2 ICP刻蚀原理

2、各向异性和各向同性刻蚀

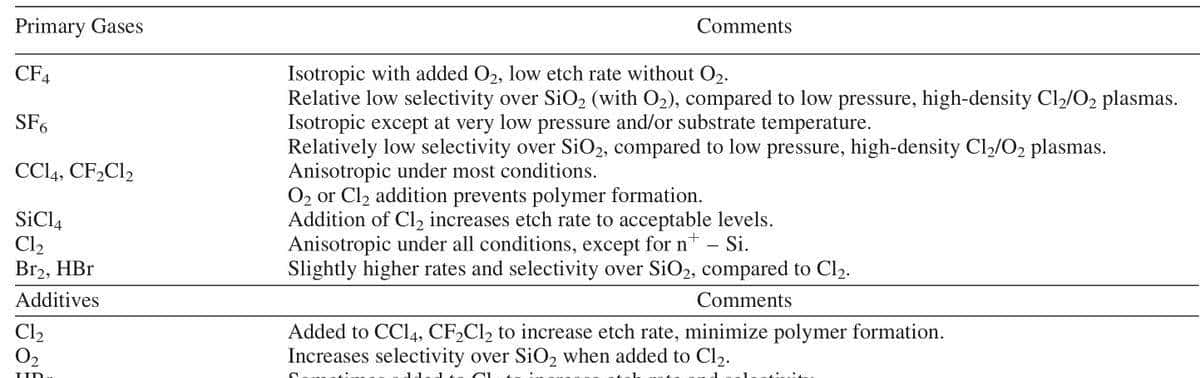

在等离子体环境下,中性气体与半导体材料的化学反应可加速。例如,用氟基或氯基化学物质在单晶或多晶硅上蚀刻图案,或在氧气等离子体中去除光致抗蚀剂薄膜。这些过程通过调节光致抗蚀剂或介电材料的掩蔽选择性,控制薄膜或基板的垂直和水平蚀刻速率,实现高保真图案转移。在某些应用中,为仅从底层不同材料上剥离一层薄膜,会采用各向同性蚀刻工艺,而在垂直方向上轮廓的形成则需要各向异性的刻蚀工艺[1]。图3为Si刻蚀中常见的刻蚀气体。

图3 Si的化学刻蚀气体

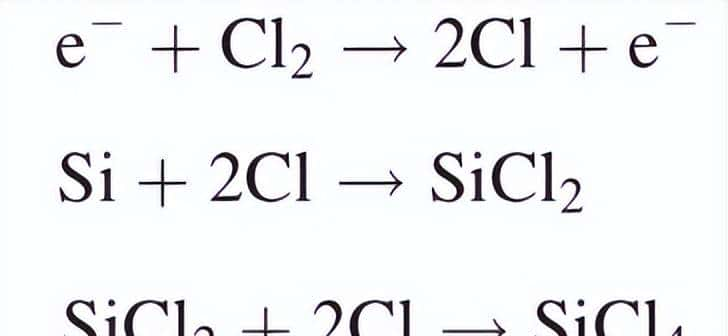

在没有大量聚合物侧壁钝化的情况下,基于氟(F)的等离子体化学刻蚀一般呈现各向同性特征。而基于氯(Cl)的等离子体刻蚀硅时,由于存在离子辅助的刻蚀机制(ion-assisted etching),可以实现较好的各向异性,形成接近垂直的侧壁而无明显下挖(undercut)。基本反应为:

图4 Cl2刻蚀反应方程

未掺杂硅在氯气中蚀刻缓慢,而重掺杂n型硅在原子氯环境下可快速蚀刻,且无需离子轰击。掺杂使蚀刻速率差异达25倍,且与掺杂剂种类无关。原子氯在未掺杂硅上吸附不破坏硅-硅键,但在n型硅上带负电,与硅形成离子键。

更多实现硅的各向异性蚀刻的方法包括:增加离子与氟的通量撞击比(如添加氩气)、添加侧壁钝化气体抑制氟原子攻击,或降低基底温度使SiF₄蚀刻产物不挥发。硅的最稳定全卤化蚀刻产物为 SiF₄(沸点-86℃)、SiCl₄(沸点57.6℃)和SiBr₄(沸点154℃)。

3、不同宽高比(Aspect Ratio)结构的匀速刻蚀方法

不同宽高比(如沟槽)的刻蚀速率会因特征尺寸不同而产生差异,导致刻蚀深度不一致,(这一般称为反应离子蚀刻滞后(ARDE),其中窄特征蚀刻较慢)。这种现象在深硅刻蚀过程中尤为明显,会导致刻蚀深度的不一致,影响器件的性能和一致性。在这里介绍了一种采用C4F8和SF6作为刻蚀气体,通过时分复用(TDM)刻蚀方法,实现了不同特征尺寸Si通孔的均匀刻蚀[2]。

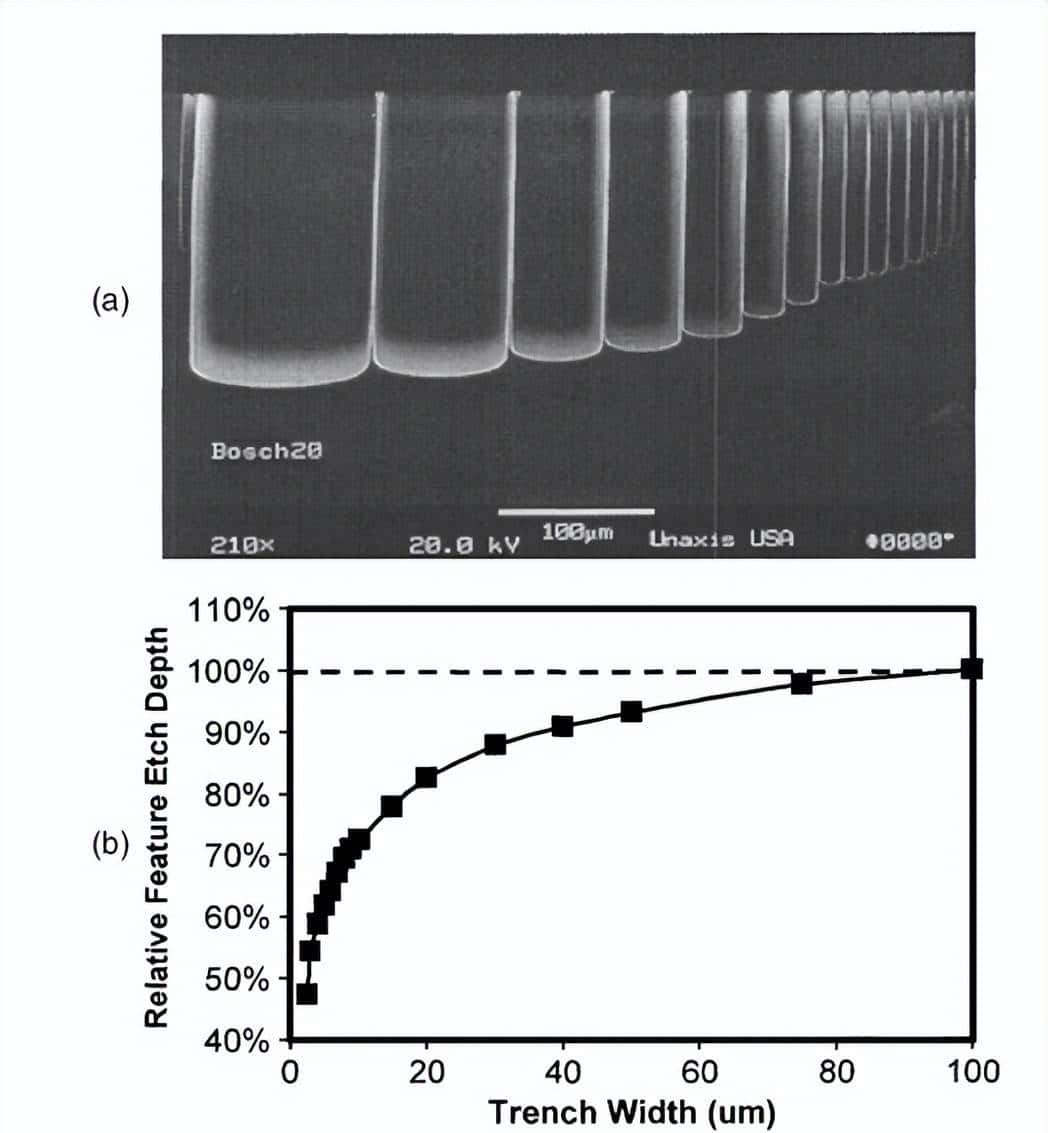

图5 不同宽高比的刻蚀深度差异

如图5所示,是不同宽度的特征结构的刻蚀速率差异。较宽的特征结构,刻蚀速率较快,刻蚀深度较大。较窄的特征尺寸,刻蚀速率较慢,刻蚀深度较小。

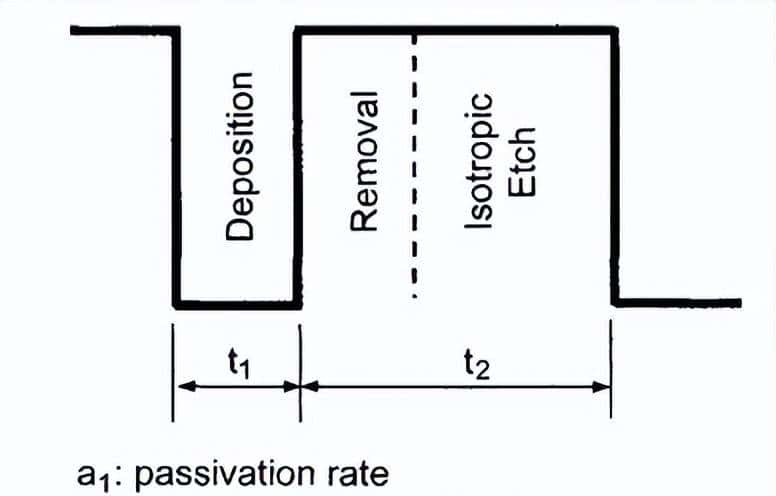

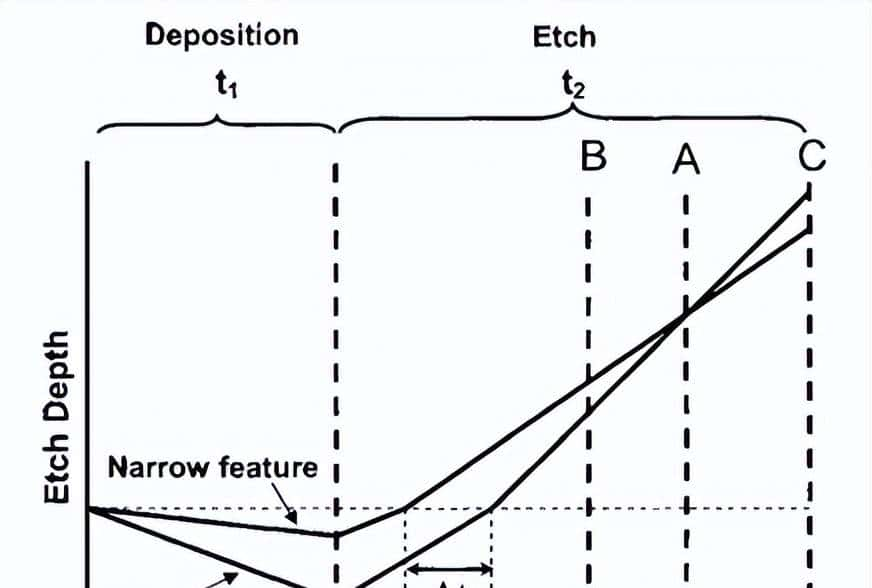

Si刻蚀的过程中,可以拆分为三个阶段,如图6所示。分别是聚合物沉积(Deposition)、聚合物去除(Removal)、硅刻蚀(Isotropic Etch)。较小宽高比的结构中,聚合物沉积速率更快,且刻蚀速率也更快。而去除步骤的速率不受宽高比的影响,所以可以增加O2使得该步骤的时间尺度保持一致。图7为不同刻蚀时间下,窄特征尺寸和宽特征尺寸刻蚀深度的对比。我们可以寻找到一个平衡的点A,以达到刻蚀深度的一致,消除ARDE滞后。

图6 三阶段模型用于TDM等离子体刻蚀工艺

图7 三阶段模型用于TDM等离子体刻蚀工艺

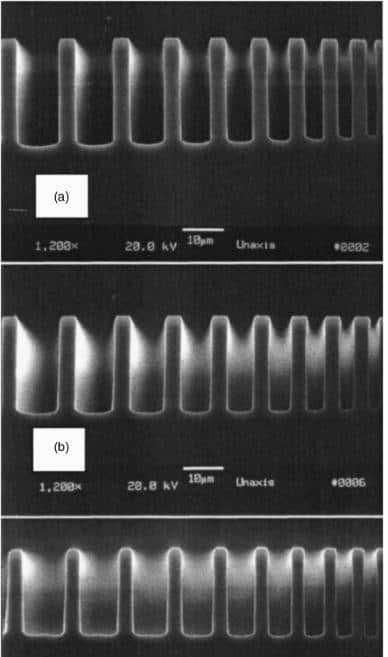

采用此方法进行优化后的刻蚀效果图如图8所示,通过控制等离子体蚀刻参数,实现了消除甚至逆转ARDE。在图8(a)中,为正常的ARDE滞后,特征宽度从10μm减小到2.5μm,深度差异接近10%。图8(b)为优化后的效果,滞后控制在2%~3%之间。图8(c)为进一步增加刻蚀步骤的时常,出现了反向的ARDE滞后。

图8 优化后的刻蚀效果图

参考文献

[1]Lai S L, Johnson D, Westerman R. Aspect ratio dependent etching lag reduction in deep silicon etch processes[J]. Journal of Vacuum Science & Technology A, 2006, 24(4): 1283-1288.

[2]Pearton S J, Norton D P. Dry etching of electronic oxides, polymers, and semiconductors[J]. Plasma processes and polymers, 2005, 2(1): 16-37.

[3]Horikoshi I. Dry etching processes and equipment[J]. Flat Panel Display Manufacturing, 2018: 319-328.

[4]Ma H J, Kim S, Kim H N, et al. Microstructural characterization and inductively coupled plasma-reactive ion etching resistance of Y2O3–Y4Al2O9 composite under CF4/Ar/O2 mixed gas conditions[J]. Scientific Reports, 2024, 14(1): 7008.

学习

收藏了,感谢分享