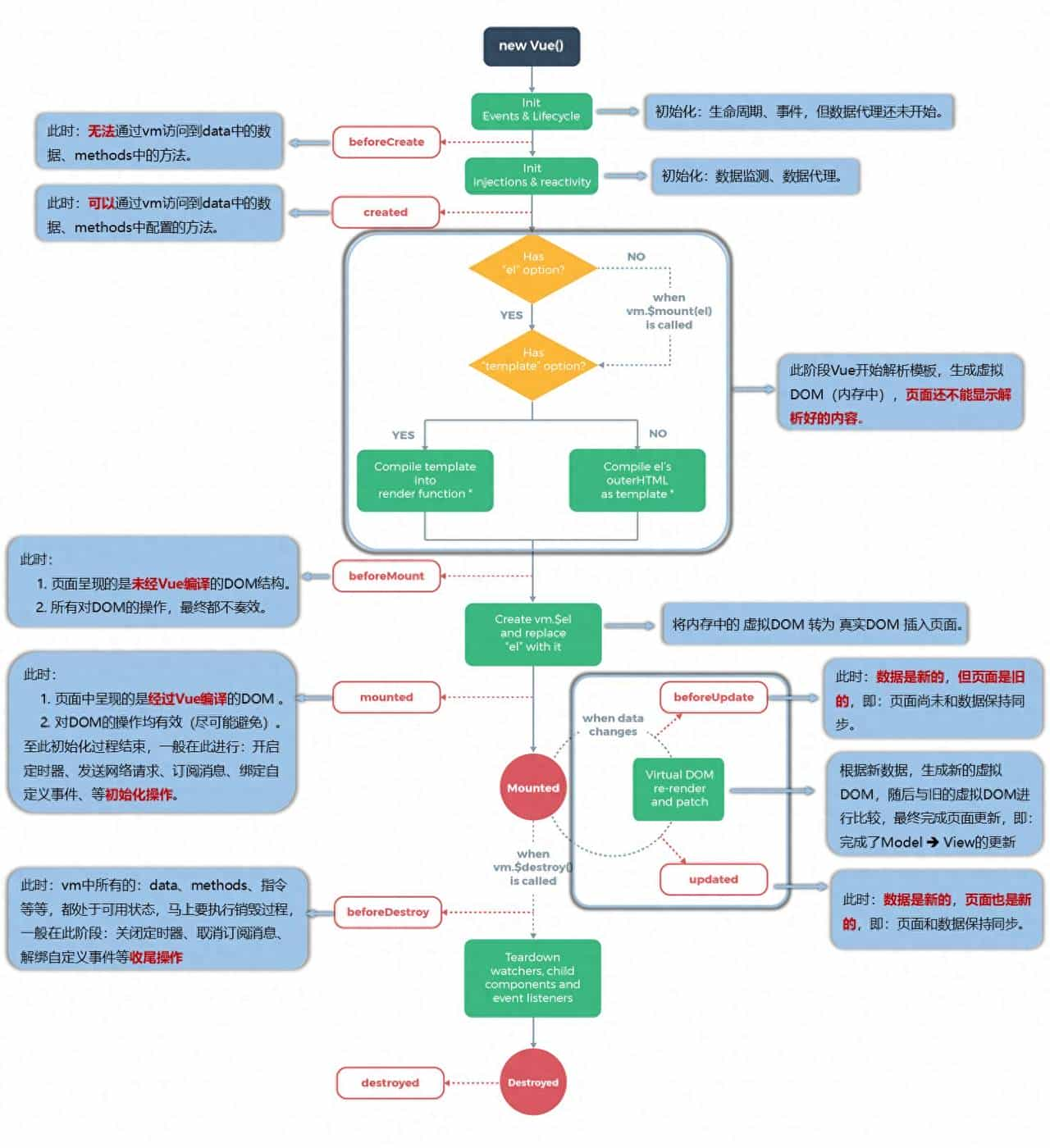

DFT 里面时钟沿设计的领域主要集中在scan chain 内,DET 与scan chain间,EDT 与IO channel间三方面

1.scan chain内

a 时钟负沿和正沿的顺序,一般选择下面的第二种,负沿在前,正沿在后

原因:

shift in 角度:例子如下图

shift out 角度:例子如下图

由上分析得出结论:采用先正后负的情况:在shift in的情况,会出现两个寄存器在一个周期的出现一样的值;对于shift out 的情况,会出现第二个负寄存的值出现丢失的情况,没办法shift 出来。

所以采用先负沿后正沿的时钟结构。

遵循的规则: 越最后capture的值的cell 越放在前面,保证不会caputre前面的一个值。

b.scan clock 允许clock mix时候,也就是跨时钟域情况

由于ck1和ck2在功能上设了异步,所以clock到达各个寄存器的时间不一样,会导致不同的时间前后。尤其是clk1 和clk2 之间的时钟沿(clock tree),导致下图两种情况出现

当clk1 后,clk2前(uesful skew)

当clk1 先,clk2后(不采用)会提前capture 新值,导致值丢失。

为防止第二种情况,解决办法是在跨时钟域的两个reg 间插latch。

插入Positive or Negative Level Latch 规则:

Launch flipflop 正沿触发,capture flipflop 也是正沿触发

这种情况需要加一个低电平传输的 Lockup Latch。也是最常见的 case。

Launch flipflop 负沿触发,capture flipflop 是正沿触发

这种情况无需加 Lockup Latch,文章前面分析过原因。

Launch flipflop 负沿触发,capture flipflop 也是负沿触发

这种情况需要加一个高电平传输的 Lockup Latch。

Launch flipflop 正沿触发,capture flipflop 是负沿触发

这种情况一个周期内传两级,会导致scan chain 数据传错,所以不能有。文章前面分析过原因。

Lockup Latch 应该加在哪里?

这里以第一种情况为例(即 Launch flipflop 和 capture flipflop 均是正沿触发的情况)。通过以上的分析得知,需要在这两个 domain 之间加 Lockup latch,才能够显著减少 hold violations。那么问题来了,这个 Lockup latch 应该加在靠近 Domain1,还是靠近 Domain 2?

靠近在 Domain2 中

将 Lockup latch 加在靠近 Domain2 中后的简易电路结构如下图所示。由于时钟树综合阶段工具会做将 Lockup latch 和 Domain2 中的寄存器做 balance,因此 clock skew 会比较小,这里假设 skew 为 0。对应的 setup 和 hold 检查波形如下图所示。

从波形图中得知,Domain1 中的 DFF 到 Lockup latch 的并没有改善(与之前 Domain1 中 DFF 和 Domain2 中 DFF 的 hold 一样大)。因此,这种 Lockup latch 加的方式是不正确的。

靠近 DOMAIN1 中

将 Lockup latch 加在靠近 Domain1 中后的简易电路结构和波形图如下图所示。

原文链接:https://blog.csdn.net/weixin_37584728/article/details/116587806

从波形图得知,Domain1 中的 DFF 到 Lockup latch 的 hold 明显得到了改善。同样 Lockup latch 到 Domain2 中的 DFF 的 hold 也没有问题。虽然 setup 检查变严格了,但是由于 scan 模式下,scan clock 是低速的。所以 setup 也没有问题。牺牲setup 换取hold 时间(hold比较难满足)

2.edt 间

https://blog.csdn.net/jinkai0822/article/details/143205053?spm=1001.2014.3001.5502

相关文章