PCIe 知识体系 500问:题目 1-100 详细答案

1. PCIe的全称是什么?它旨在替代哪些传统的总线标准? 答:

全称:Peripheral Component Interconnect Express。旨在替代的标准:

PCI (Peripheral Component Interconnect):最直接的替代目标。PCI是32/64位并行共享总线,其架构限制了频率和带宽的提升,且存在信号同步和干扰问题。AGP (Accelerated Graphics Port):专为显卡设计的专用并行总线。PCIe x16提供了更高的带宽和更好的通用性,成为新的图形接口标准。PCI-X (PCI Extended):PCI的高速增强版,主要用于服务器。它虽提升了频率和宽度,但仍未摆脱并行共享总线的根本性缺陷(信号完整性、扩展性)。PCIe通过串行点对点架构实现了对其的超越和替代。

技术范式转变:PCIe的替代不仅是速度提升,更是架构革命:从并行到串行,从共享总线到点对点交换,同时在软件层面保持了与PCI的兼容性。

2. 描述PCIe的拓扑结构,并列出其中的关键组件。 答:

拓扑:非对称的、基于交换(Switch)的星形树状结构(Hierarchical Star)。Root Complex是树的根,Switch是分支节点,Endpoint是叶子节点。关键组件:

Root Complex (RC):连接CPU/内存子系统与PCIe层次结构的芯片组或SoC部件。是生成PCIe事务的根,也是枚举过程的起点。Switch:智能多端口连接和路由设备,提供扇出(Fan-out)能力,允许多个设备共享一个上游端口。内部由多个虚拟的PCI-to-PCI桥组成。Endpoint (EP):实现特定功能的PCIe设备(如GPU、NIC、SSD)。可以发起和响应PCIe事务。PCIe/PCI Bridge:用于连接旧式PCI/PCI-X总线的桥接设备,现已不常见。

3. 什么是Root Complex (RC)?它在系统中扮演什么角色? 答:

定义:RC是处理器和内存子系统与PCIe架构之间的接口,是PCIe拓扑的根。核心角色:

事务代理:代表CPU发起存储器读写事务到EP;代表EP完成对系统内存的访问。系统资源管理者:是系统内存和I/O空间的“所有者”。枚举起点:是总线0的持有者,由它开始配置PCIe系统。路由与仲裁:在其多个下行端口间进行流量路由和仲裁。高级功能中心:集成错误处理(AER)、电源管理(PM)、虚拟化支持等系统级功能。

4. 什么是Endpoint (EP)?列举几种不同类型的Endpoint。 答:

定义:PCIe设备的基本类型,是实现特定功能(如图形、存储、网络)的硬件实体。类型:

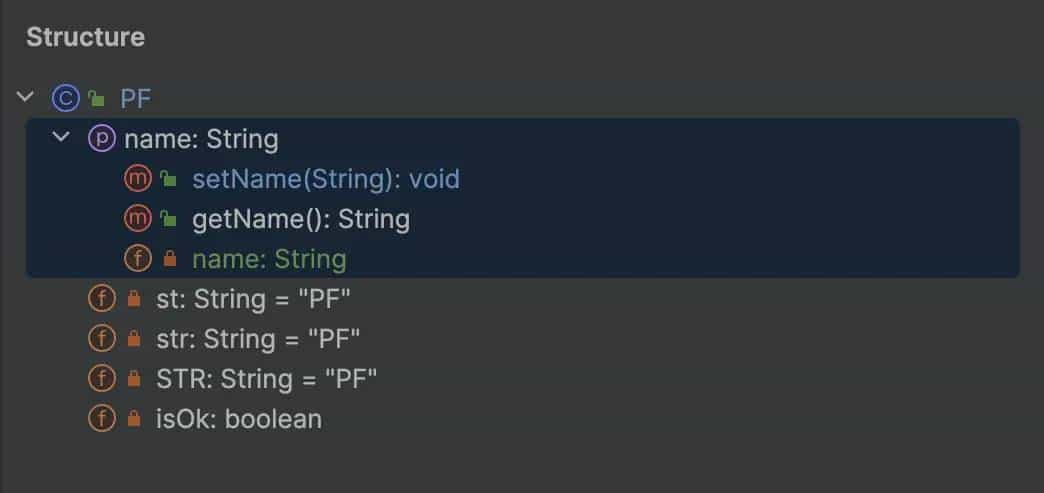

传统Endpoint (Legacy Endpoint):支持PCI兼容性功能(如IO空间、INTx中断)的设备。PCIe Endpoint:原生PCIe设备,可能不支持某些传统PCI特性。Root Complex Integrated Endpoint (RCIEP):物理上集成在RC(如SoC内)的端点,在逻辑上仍被视为一个Endpoint。SR-IOV Endpoint:支持单根I/O虚拟化的端点,能呈现出一个物理功能(PF)和多个虚拟功能(VF)。

5. PCIe Switch的核心功能是什么?它是如何实现数据路由的? 答:

核心功能:连接和扩展。将一个上游端口(靠近RC)连接到多个下游端口(靠近EP),并在这些端口间高效地路由数据包。路由方式:Switch内部包含一个路由逻辑和多个虚拟PCI-to-PCI桥。它检查每个传入TLP(事务层数据包)头部的字段,基于以下方式决定从哪个端口转发:

地址路由 (Address Routing):用于存储器请求。Switch根据TLP中的地址判断目标设备位于哪个下游端口。ID路由 (ID Routing):用于配置请求和完成包。Switch根据TLP中的总线/设备/功能号(BDF) 判断路由路径。隐式路由 (Implicit Routing):用于某些消息TLP(如广播消息),根据消息类型本身进行路由。

6. 解释PCIe的Link和Lane概念。一个x16 Link由多少条Lane组成? 答:

Lane:PCIe互连的最基本物理单元。一个Lane由两对差分信号线(共4根线)组成:一对用于发送(TX),一对用于接收(RX)。Link:两个PCIe端口之间的双工通信通道。一个Link由1个或多个Lane捆绑(Bonded)而成,以提供更高的带宽。x16 Link:由16条Lane组成。通常用于需要极高带宽的设备,如图形卡(GPU)和高速网卡。

7. 每条PCIe Lane由多少根差分信号线组成?其作用是什么? 答:

数量:4根线(2对)。作用:

一对差分发送 (TX+ / TX-):将数据从设备发送出去。一对差分接收 (RX+ / RX-):从外部接收数据。

差分信号优点:通过比较两根线之间的电压差来传输信号,能有效抵抗外部共模噪声,允许更高的工作频率。

8. 与传统PCI的并行总线相比,PCIe的串行差分信号有何优势? 答:

更高带宽/频率:串行链路避免了并行总线因线间长度不匹配导致的时钟偏移(Skew) 问题,可以运行在极高频率(GHz级别)。更强抗干扰能力:差分信号对共模噪声有天然的免疫力。更低引脚数/更小体积:用少量线对即可实现高带宽,减少了连接器尺寸和PCB布线复杂度。内嵌时钟:数据流中嵌入了时钟信息(通过编码),无需单独的时钟线,消除了时钟-数据之间的偏移问题。支持热插拔:物理连接更简单,易于实现热插拔。可扩展性:通过增加Lane数(x1, x2, x4, x8, x16, x32)轻松扩展带宽。

9. PCIe是半双工还是全双工通信? 答: 全双工通信。每个Lane都包含独立的发送和接收通道,因此一个设备可以同时向链路的另一端发送数据和接收数据。

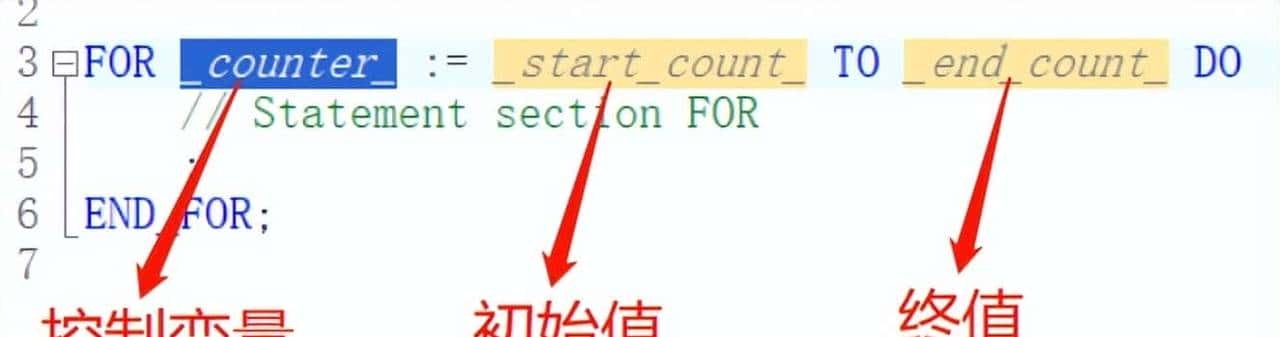

10. 两个Endpoint能否直接通信?为什么? 答: 在标准PCIe拓扑中,不能直接通信。所有通信都必须经过Root Complex。如果一个Endpoint想和另一个Endpoint通信,路径通常是:EP1 -> Switch -> RC -> Switch -> EP2。RC作为系统的核心,负责所有内存访问的协调和路由。然而,通过非透明桥(NTB) 或Peer-to-Peer(P2P)等特殊技术,可以在特定条件下实现Endpoint间的直接数据传输,但这需要硬件和软件的特殊支持,并非基础规范的要求。

11. 什么是PCIe的传输速率单位GT/s?它与GB/s有何区别? 答:

GT/s (GigaTransfers per second):表示每秒传输的次数。它指的是原始物理层符号的传输速率。GB/s (GigaBytes per second):表示每秒传输的有效数据字节数。区别与计算:

GT/s是物理层速率,包含了编码开销。GB/s是有效数据速率,需从GT/s扣除编码开销和协议开销后计算得出。例如:PCIe 3.0的速率是8 GT/s。采用128b/130b编码(效率 = 128⁄130 ≈ 98.46%)。 则每Lane的有效数据速率 = (8 GT/s * (128⁄130)) / 8 bits/byte = ≈ 0.985 GB/s。 一个x16链路的双向带宽 = 0.985 GB/s/Lane * 16 Lanes * 2 (全双工) = ≈ 31.5 GB/s。

12. 计算PCIe 3.0 x8链路的有效数据传输带宽(考虑编码开销)。 答:

PCIe 3.0速率:8 GT/s编码方案:128b/130b,效率 = 128⁄130每Lane有效数据速率 = (8 GT/s * (128⁄130)) / 8 bits/byte ≈ 0.9846 GB/sx8链路单向带宽 = 0.9846 GB/s * 8 = 7.877 GB/sx8链路双向带宽 = 7.877 GB/s * 2 = 15.754 GB/s

13. 计算PCIe 5.0 x16链路的有效数据传输带宽。 答:

PCIe 5.0速率:32 GT/s编码方案:128b/130b,效率 = 128⁄130每Lane有效数据速率 = (32 GT/s * (128⁄130)) / 8 bits/byte ≈ 3.9385 GB/sx16链路单向带宽 = 3.9385 GB/s * 16 = 63.015 GB/sx16链路双向带宽 = 63.015 GB/s * 2 = 126.03 GB/s

14. 从Gen1到Gen6,列出每一代PCIe的原始比特率、编码方案和编码效率。 答:

| 代次 | 原始比特率 (GT/s) | 编码方案 | 编码效率 |

|---|---|---|---|

| Gen1 | 2.5 | 8b/10b | 80% (8⁄10) |

| Gen2 | 5.0 | 8b/10b | 80% (8⁄10) |

| Gen3 | 8.0 | 128b/130b | ~98.46% (128⁄130) |

| Gen4 | 16.0 | 128b/130b | ~98.46% (128⁄130) |

| Gen5 | 32.0 | 128b/130b | ~98.46% (128⁄130) |

| Gen6 | 64.0 (PAM4) | 1b/1b + FLIT | ~98.24% (256⁄261) |

15. 为什么从Gen3开始需要更复杂的编码方案(128b/130b vs 8b/10b)? 答: 为了降低编码开销,提升有效带宽。

8b/10b:开销为 20% (2⁄10)。在高速率下,这个开销变得无法接受。128b/130b:开销仅为 ~1.54% (2⁄130)。这使得在几乎相同的物理信号速率下,有效数据吞吐量大幅提升。128b/130b编码的实现更复杂,需要更大的逻辑块和缓冲区来处理128位的数据块,但在Gen3及以上的高速时代,这种权衡是绝对值得的。

16. 什么是Lane Reversal?它在PCB布线中有何实用价值? 答:

定义:Lane反转。指在PCB布线时,故意将Link中的Lane物理连接顺序颠倒(例如,上游端口的Lane0连接到下游端口的Lane3,Lane1连接到Lane2等)。实用价值:极大简化PCB布线。设计师可以更灵活地走线,避免信号线交叉,缩短走线长度,改善信号完整性,从而降低PCB的层数和制造成本。链路训练过程会自动检测并纠正这种反转,对软件完全透明。

17. 什么是Polarity Inversion?它的作用是什么? 答:

定义:极性反转。指在PCB布线时,将差分信号对内的两根线(+和-)交换连接。作用:解决PCB布线时的偶然错误。如果设计师不小心将一对差分线接反了,接收端的极性反转电路可以自动检测并纠正这个错误,无需重新制作PCB。这也简化了连接器的设计。

18. Lane Reversal和Polarity Inversion有哪些限制? 答:

Lane Reversal:通常是按顺序的。不能是随机的映射,必须是一个连续的、顺序反转的集合(例如,Lane [0:3] 反转为 [3:0])。所有Lane必须参与反转。Polarity Inversion:是以每个Lane为单位的。每个Lane可以独立决定是否进行极性反转。

19. 什么是PCIe Bifurcation?它的主要应用场景是什么? 答:

定义:链路拆分。指将Root Complex或Switch的一个物理上的宽端口(如x16)在硬件上拆分成多个逻辑上的窄端口(如x8x8或x4x4x4x4)的能力。应用场景:主要应用于主板设计。允许用户在一条x16插槽上安装多个设备。例如:

将x16插槽拆分为两个x8,以安装两块显卡(NVLink/SLI)或一块显卡和一块高速NVMe SSD卡。将x16插槽拆分为四个x4,以安装多个NVMe SSD扩展卡。该功能需RC、BIOS和主板的协同支持。

20. PCIe设备有哪些不同的地址空间? 答: PCIe设备支持三种CPU可寻址的空间:

存储器地址空间 (Memory Address Space):用于一般的数据传输(如显卡帧缓存、网卡数据缓冲区)。这是最主要的地址空间。I/O地址空间 (I/O Address Space):用于与x86架构兼容的 legacy 设备。现代PCIe设备应避免使用此空间,它正在被淘汰。配置地址空间 (Configuration Address Space):用于发现、配置和管理PCIe设备。操作系统通过此空间配置设备的BAR、分配资源、启用功能等。

21. 解释Posted与非Posted事务的根本区别。请举例说明。 答:

Posted(发布)事务:

特点:发起方发出请求后不期望收到任何确认或完成包。它是“发射后不管”的。目的:提高写操作的效率,减少延迟。示例:存储器写(MWr)、消息(Message)。

Non-Posted(非发布)事务:

特点:发起方发出请求后必须等待一个完成包(Completion, Cpl或CplD)返回,以确认请求已被处理。目的:确保读操作和数据完整性,需要返回数据或状态。示例:存储器读(MRd)、I/O读写(IORd/IOWr)、配置读写(CfgRd/CfgWr)。

22. 为什么存储器写是Posted事务,而存储器读是Non-Posted事务? 答: 这是出于性能和协议效率的考量。

存储器写 (Posted):写操作的目标是最终将数据送达目的地。只要数据被接收方正确接收(由数据链路层的ACK保证),发起方就可以继续后续工作,无需等待数据被最终处理,这极大提升了写操作的吞吐量和效率。存储器读 (Non-Posted):读操作的目的是获取数据。发起方必须等待包含所请求数据的完成包返回,否则无法继续执行依赖于该数据的指令。因此,它必须是请求-响应模式。

23. 什么是流量控制(Flow Control)?其目的是什么? 答:

定义:一种基于信用(Credit) 的机制,用于确保发送方只有在接收方有足够缓冲区来存放TLP时,才会发送该TLP。目的:

防止缓冲区溢出:从根本上避免接收方因为来不及处理数据而导致数据丢失。消除重传带来的性能损失:由于确保了TLP只会被成功接收,数据链路层无需因缓冲区满而进行重传,提升了效率。实现零丢包:是PCIe高可靠性的关键机制之一。

24. 简述流量控制信用(Credit)机制的基本原理。 答:

初始化:链路训练完成后,每个接收器都会通过DLLP(数据链路层包)向其对应的发送器通告其初始信用量(例如:我有N个单位的缓冲区)。发送规则:发送器在发送一个TLP前,会检查其拥有的对应类型(如Posted, Non-Posted, Completion)的信用数量是否足够覆盖这个TLP的大小。信用消耗:如果信用足够,发送TLP,并扣除相应的信用值。信用归还:接收器处理完TLP(将数据从缓冲区取走)后,会发送一个“更新信用”DLLP给发送器。信用补充:发送器收到DLLP后,增加相应的信用值。 通过这个“借”和“还”的循环,发送方的发送速率被接收方的处理能力所控制。

25. 什么是虚拟通道(VC)?它的作用是什么? 答:

定义:虚拟通道是物理链路上的独立逻辑通信路径。每个VC有自己独立的流量控制缓冲区和信用机制。作用:

服务质量 (QoS):允许为不同类别的流量(如等时传输Isochronous traffic和普通异步流量)分配不同的VC和优先级,防止一种流量阻塞另一种流量。避免协议死锁:通过为完成包(Completion)和请求包(Request)提供独立的VC,可以打破某些潜在的请求-响应循环依赖造成的死锁情况。

26. 描述系统启动时PCIe设备枚举的基本过程。 答: 枚举是系统(BIOS/OS)发现PCIe拓扑结构并配置所有设备的过程。

从Bus 0开始:RC从Bus 0开始扫描。扫描每个设备:对每个可能的设备号(Device Number)和功能号(Function Number),读取其Vendor ID寄存器。

如果Vendor ID不是0xFFFF(表示设备存在),则对该设备进行配置。

配置设备:读取设备的BAR,了解其需要多大的内存/IO空间,然后由系统分配一段空闲的地址范围并写入BAR。处理桥设备:如果发现一个设备是桥(Switch的下游端口或PCI桥),则:

分配一个新的未使用的总线号(Bus Number)给桥下游的次级总线(Secondary Bus)。将这个新总线号写入桥的配置寄存器。递归枚举:将这个新总线作为起点,重复步骤1-4,继续扫描下游设备。

完成:当所有总线都被扫描后,整个PCIe拓扑结构就被建立起来,所有设备的资源都已分配。

27. BIOS/UEFI在PCIe枚举过程中负责什么? 答: BIOS/UEFI负责前期的硬件枚举和资源分配。

执行上述枚举过程,建立硬件拓扑图。为所有PCIe设备的BAR分配临时或最终的资源(内存、IO空间、中断线)。配置PCIe设备的基本运行参数(如MPS, MRRS)。将控制权移交给操作系统前,提供一个清晰的设备列表和资源分配表(ACPI表格)。

28. 操作系统如何参与PCIe资源的分配和管理? 答: 操作系统是资源的最终管理者和设备的驱动者。

可能重新分配资源:OS可能会根据自身的内存管理策略,重新分配BIOS已分配的地址空间,以优化布局。加载驱动程序:根据设备的Vendor ID和Device ID,加载对应的设备驱动程序。提供用户接口:OS提供API和用户界面,让应用程序和用户能与PCIe设备交互。高级功能管理:管理电源管理、错误报告、热插拔等高级功能。

29. 什么是PCIe的Max_Payload_Size (MPS)?它如何影响性能? 答:

定义:最大有效载荷大小。指一个TLP所能携带的数据载荷的最大字节数。常见值有128B, 256B, 512B等。对性能的影响:

大MPS:减少了协议开销(TLP头、CRC等)占总传输数据的比例,提升了传输大块数据时的效率。小MPS:有利于降低延迟,因为小包可以更快地被组装和发出。系统中的所有设备(RC, Switch, EP)会协商一个共同支持的MPS值。不匹配的MPS设置会导致性能下降。

30. 什么是Max_Read_Request_Size (MRRS)?它如何影响性能? 答:

定义:最大读请求大小。指发起读请求的设备一次所能请求的最大数据字节数。对性能的影响:

大MRRS:允许一个读请求就能获取大量数据,减少了完成包的数量和事务处理的开销,显著提升读操作的吞吐量。小MRRS:如果需要读取大量数据,必须拆分成多个小读请求,增加了延迟和协议开销,性能差。应始终将MRRS设置为系统支持的最大值(通常为512B或4096B),以最大化读性能。

31. 解释ECRC和LCRC的区别及其各自的作用。 答:

LCRC (Link CRC):

作用范围:单跳链路。由发送端的数据链路层生成,由接收端的数据链路层校验。目的:保护TLP在穿过单个链路时的完整性。如果校验失败,接收端会通过NAK DLLP请求发送端重传该TLP。这是PCIe链路可靠性的基础。

ECRC (End-to-End CRC):

作用范围:从发起方到完成方的整个路径。由发起方的事务层生成,由最终接收方( Completer )的事务层校验。目的:保护TLP在穿过整个系统(可能经过多个Switch和桥)过程中的完整性。用于高级错误报告(AER),检测在中间组件中可能发生的错误。关系:一个TLP可以同时拥有LCRC和ECRC。LCRC用于链路级可靠性,ECRC用于端到端数据完整性检查。

32. PCIe协议规范由哪个组织维护和发布? 答: 由 PCI-SIG (Peripheral Component Interconnect Special Interest Group) 维护和发布。这是一个由业界多家公司组成的联盟,负责定义和发展PCIe标准。

33. 区分不同尺寸的PCIe卡(如x1, x4, x8, x16)及其典型应用。 答:

x1:短插槽。用于对带宽要求不高的扩展卡,如声卡、千兆网卡、低速采集卡。x4:中等长度。常用于NVMe SSD、万兆网卡、RAID控制卡。x8:较长。用于中高端网卡(25G/40G)、高性能SSD、专业视频采集卡。x16:最长。主要用于高端图形卡(GPU),也用于高速计算加速卡(如FPGA)和顶级NVMe SSD阵列卡。注意:物理尺寸通常与链路宽度对应,但并非绝对。有些x16插槽可能只提供x8或x4的电信号连接(为了成本),反之亦然(用延长板实现x16物理尺寸的x4卡)。

34. 什么是NVMe?它与PCIe是什么关系? 答:

NVMe (Non-Volatile Memory Express):是一种高效的主机控制器接口规范(协议),专为基于PCIe的固态硬盘(SSD)设计。关系:NVMe是运行在PCIe之上的高层协议。PCIe为NVMe SSD提供了物理层和链路层的高速连接通道,而NVMe定义了操作系统如何与SSD控制器进行通信(队列、命令集等),充分发挥PCIe的低延迟和高并行性优势。可以说,PCIe是“高速公路”,而NVMe是高效的“交通规则”。

35. 描述一个完整的PCIe事务(如存储器读)所需要经历的协议层。 答: 以存储器读(MRd)为例,它需要遍历所有三层:

事务层 (Transaction Layer – 发起方):

生成存储器读请求TLP,包含地址、长度(Tag、TC等字段)。将该TLP传递给数据链路层。

数据链路层 (Data Link Layer – 发起方):

为TLP添加序列号和LCRC。将其传递给物理层。

物理层 (Physical Layer – 发起方):

对TLP进行编码(如128b/130b)。通过差分信号将数据串行化并发送到链路上。

物理层 (Physical Layer – 接收方):

解串并解码接收到的比特流。将恢复出的数据包传递给数据链路层。

数据链路层 (Data Link Layer – 接收方):

校验LCRC。若正确,返回ACK DLLP;若错误,返回NAK DLLP请求重传。将校验正确的TLP剥离序列号和LCRC,传递给事务层。

事务层 (Transaction Layer – 接收方):

解读TLP,执行读操作(从本地内存中获取数据)。生成一个带数据的完成包(CplD),并沿原路返回给发起方。(完成包CplD会经历相反的过程,最终到达发起方的事务层)。

36. 什么是MSI中断?相比传统中断有何优势? 答:

MSI (Message Signaled Interrupt):一种通过写入存储器地址来产生中断的机制。设备不是通过拉高专用的中断线(INTx)来请求中断,而是向RC指定的一个存储器地址写入一个特定的数据值(Message)。这个写操作会形成一个存储器写TLP。优势:

无共享线问题:每个设备有自己的唯一消息地址和数据,彻底消除了中断线共享带来的冲突和性能问题。更多中断向量:MSI最多可支持32个中断向量,MSI-X支持更多(2048个),允许一个设备为不同事件申请不同中断,减少中断处理程序的判断开销。更低延迟:中断信息作为Posted写请求发送,效率高于边带信号。更好的可扩展性:易于在多处理器系统中进行中断路由和负载均衡。

37. 什么是MSI-X中断?相比MSI有何优势? 答:

MSI-X:是MSI的扩展版本。优势:

更多向量:支持最多2048个独立中断向量(MSI只有32个)。灵活的表结构:中断信息(地址和数据)存储在一个位于存储器空间的表中(MSI寄存器在设备的配置空间中)。这使得动态分配和管理中断变得更容易。每个向量独立屏蔽:每个中断向量都可以被独立屏蔽(MSI只能屏蔽所有)。更好的性能:特别适合需要大量精细中断的高性能设备(如网卡、NVMe SSD)。

38. 简述PCIe电源管理的基本框架(设备状态 vs 链路状态)。 答: PCIe电源管理是一个二维模型:

设备电源状态 (D-states):关注设备本身的功耗。

D0:全功耗工作状态。D1:低功耗状态(可选),上下文部分丢失。D2:更深低功耗状态(可选),上下文大部分丢失。D3hot:软件发起的低功耗状态,电源仍存在,上下文完全丢失。D3cold:主要电源被移除,仅保留辅助电源(Vaux)用于唤醒,上下文完全丢失。

链路电源状态 (L-states):关注物理链路的功耗。

L0:全功耗工作状态。L0s:快速低功耗状态(快速进入/退出),用于节省空闲时的功耗。L1:更深低功耗状态(较慢进入/退出),节省更多功耗。L2/L3 Ready:过渡状态。L3:链路关闭,电源完全移除。

关系:设备状态和链路状态相互关联但又相对独立。例如,设备进入D3hot状态通常会导致链路进入L1或L2/L3状态。

39. 什么是ASPM?它有哪些模式? 答:

ASPM (Active State Power Management):活动状态电源管理。一种由硬件自动控制的节能机制,当链路处于活动状态但空闲时,无需软件干预,自动将链路切换到低功耗状态(L0s或L1)。模式:

L0s Entry/Exit:超低延迟的节能状态。仅接收端关闭,退出延迟极短(μs),适用于短时间空闲。L1 Entry/Exit:更深节能状态。收发端都关闭,退出延迟较长(几μs到几十μs),适用于较长时间空闲。

40. 什么是LTR机制?它对系统功耗和性能有何益处? 答:

LTR (Latency Tolerance Reporting):延迟容忍报告。允许Endpoints向Root Complex报告它们对服务延迟的容忍程度(即它可以忍受多长的睡眠而不影响性能)。益处:

功耗:RC的电源管理单元可以根据所有设备的LTR信息,智能地决定何时可以让整个系统或部分组件进入更深、更省电的睡眠状态,而不会损害性能。性能:避免了RC过于激进地进入节能状态而导致设备被唤醒时体验到的性能下降(延迟增加)。LTR提供了数据来优化睡眠策略。

41. 什么是OBFF机制?它的工作原理是什么? 答:

OBFF (Optimized Buffer Flush/Fill):优化缓冲区刷新/填充。一种机制,允许系统(RC)向设备发出提示,告知它们现在是一个进行大量数据传输的好时机(或坏时机)。工作原理:系统通过一个特殊的Message TLP向设备发送提示。

“Flush”提示:告诉设备“现在系统很忙,不适合发送数据”。设备可以暂时缓存数据,稍后再发。“Fill”提示:告诉设备“现在系统空闲,是发送数据的好时机”。设备可以趁机将缓存的数据发出。

目的:通过协调设备的流量爆发时间,使系统能更长时间地保持在低功耗状态,从而节省整体系统功耗。

42. 解释PCIe配置空间的总大小和布局。 答:

总大小:每个PCIe功能(Function)有4096 Bytes的配置空间。这比传统PCI的256字节大得多。布局:

前256字节:称为PCI兼容性配置空间。其布局与PCI标准完全相同,以确保软件兼容性。后3840字节:称为PCIe扩展配置空间。用于存放PCIe特有的能力结构(Capability Structures),如PCIe Capability, MSI-X Capability, AER Capability等。

43. 什么是Type 0和Type 1配置空间头部?它们分别对应什么设备? 答:

Type 0头部:用于非桥设备,即Endpoints。它的配置空间寄存器用于配置Endpoint自身的功能。Type 1头部:用于桥设备,即Switches的各端口和PCIe-to-PCI bridges。它包含用于路由和管理下游总线的寄存器(如Primary, Secondary, Subordinate Bus Number寄存器)。

44. 什么是Base Address Register (BAR)?系统如何确定BAR的大小和类型? 答:

BAR:基地址寄存器。位于配置空间的开头。它定义了设备需要被映射到系统存储器或I/O空间中的地址范围及其大小。确定大小和类型的步骤(软件执行):

向BAR写入全1 (

0xFFFFFFFF

bit0 = 1:I/O空间 BAR(32位)。bit0 = 0, bit2-1 = 00:32位存储器空间 BAR。bit0 = 0, bit2-1 = 10:64位存储器空间 BAR。

读回值中低位的0:这些连续的0表示该设备请求的地址空间大小。软件可以计算出大小 = 2^(number of zeros)。软件随后分配一个适当大小和对齐的地址块,并将该基地址写回BAR。

45. 什么是Capability Structure?它是如何组织的? 答:

Capability Structure:能力结构。是位于PCIe扩展配置空间中的一种数据结构,用于描述和支持PCIe设备的各种高级功能(如MSI, PCIe, AER, ATS等)。组织方式:以链表形式组织。

每个能力结构都有一个Capability ID(标识功能类型)和一个Next Pointer(指向下一个能力结构的偏移地址)。配置空间中的一个指针(

Capabilities Pointer

46. 列出至少5种常见的PCIe Capability Structure。 答:

PCI Express Capability:必须有的结构,描述PCIe链路本身的能力和状态(链路速度、宽度、最大负载等)。MSI Capability:支持Message Signaled Interrupts。MSI-X Capability:支持扩展的Message Signaled Interrupts。Advanced Error Reporting (AER) Capability:支持高级错误报告和日志记录。Virtual Channel (VC) Capability:支持虚拟通道。Device Serial Number Capability:提供设备的唯一序列号。Power Management (PM) Capability:支持PCI Power Management。Access Control Services (ACS) Capability:支持访问控制服务,用于虚拟化隔离。

47. 什么是Enhanced Configuration Access Mechanism (ECAM)? 答:

ECAM:增强型配置访问机制。是访问PCIe扩展配置空间(4KB)的标准方法。工作原理:系统硬件将CPU对一段特定物理地址范围(由ACPI表格定义)的访问,转换为对PCIe配置空间的访问。地址组成:一个ECAM地址直接编码了总线号(Bus)、设备号(Device)、功能号(Function) 和寄存器偏移量(Register Offset)。CPU通过简单的存储器读写指令即可访问任何PCIe设备的任何配置寄存器,无需复杂的IO端口操作。

48. 在枚举过程中,如何确定PCIe桥下游的总线号范围? 答: 这是一个递归过程:

当枚举软件(BIOS)发现一个桥(Type 1头部设备)时,它会分配一个起始总线号给该桥的次级总线(Secondary Bus)寄存器。软件然后开始扫描这个新总线(比如Bus Y)。如果在这个新总线上又发现了下游桥,软件会:

再分配一个新的总线号(Y+1)给这个新下游桥的次级总线。然后继续扫描Bus Y+1。

当扫描完一个分支的所有下游设备后,软件将最后一个被使用的总线号写入最初那个桥的下属总线(Subordinate Bus)寄存器。最终结果:桥的配置空间中的三个寄存器定义了其管理的总线范围:

Primary Bus

Secondary Bus

Subordinate Bus

49. 什么是ARI(Alternative Routing-ID Interpretation)?它解决了什么问题? 答:

ARI:替代路由ID解析。是一种扩展PCIe路由机制的特性。解决的问题:传统PCIe寻址使用BDF(Bus, Device, Function),其中Device是5位(最多32个设备),Function是3位(最多8个功能)。ARI取消了Device Number字段,将其位宽合并到Function字段中,从而将Function字段扩展为8位(最多支持256个功能)。好处:允许一个物理设备支持远多于8个的功能(VF),极大地增强了SR-IOV等技术的扩展能力,无需使用多个Device ID来虚拟多个设备。

50. 什么是PCIe的设备序列号(Device Serial Number)功能? 答:

定义:一个可选的Capability Structure(ID为0x03),它提供一个全球唯一的标识符(EUl-64格式)给PCIe设备。作用:

唯一标识:即使在有多个完全相同型号的设备系统中,也能唯一地识别每个物理设备。库存和管理:便于资产跟踪和管理。软件许可:可用于将软件许可证与特定硬件绑定。调试:在复杂系统中精确定位物理设备。

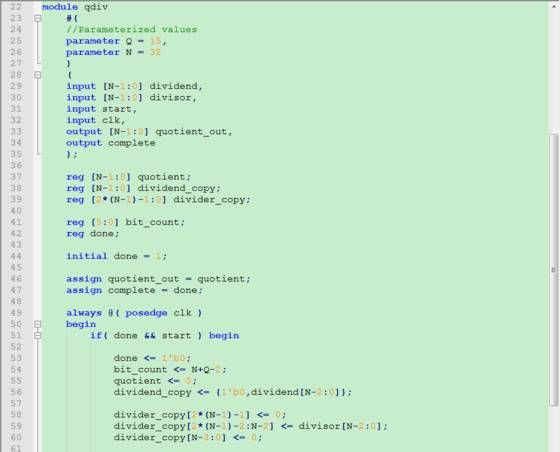

51. PCIe物理层的主要子块有哪些?简述其功能。 答: PCIe物理层分为两个逻辑子层:

物理逻辑子层 (Physical Logic Sublayer):

负责数字功能。发送端:从数据链路层接收数据,进行** scrambling(加扰)** 和编码(8b/10b 或 128b/130b),然后传递给电气子层。接收端:从电气子层接收数据,进行解码和解扰,将恢复的数据包传递给数据链路层。其他功能:负责弹性缓冲区(Elastic Buffer) 管理、链路训练状态机控制、有序集(Ordered Set)的生成和检测。

电气子层 (Electrical Sublayer):

负责模拟功能。发送端:将逻辑子层送来的并行数据串行化(Serializer),经过均衡(Equalization) 和驱动后,通过差分线对发送出去。接收端:从差分线对接收信号,进行均衡,时钟数据恢复(CDR – Clock Data Recovery),最后解串(Deserializer) 成并行数据送给逻辑子层。

52. 描述差分信号的优点,它是如何抵抗共模噪声的? 答:

优点:

抗共模噪声能力强(见下文)。抗电磁干扰(EMI) 能力更强:由于两根线电流方向相反,产生的磁场会相互抵消,辐射更低。时序精度高:信号切换基于交叉点电压,对噪声不敏感,抖动更低。

抗共模噪声原理:差分信号接收器只关心两条线(D+和D-)之间的电压差(Vdiff = V_D+ – V_D-),而不关心它们对地的绝对电压。当共模噪声(如电源噪声)同时耦合到两条线上时,两条线的电压会同时升高或降低,但它们之间的电压差保持不变,从而噪声被有效抑制。

53. 什么是发送器(TX)的De-emphasis?为什么需要它? 答:

定义:去加重。是一种预失真技术。在发送一个比特跳变(如0->1或1->0)后,发送器会在后续几个连续相同的比特位上有意降低发送信号的幅度。原因:信号在通道(PCB走线、连接器)中传输时,高频分量比低频分量衰减得更严重(通道的“低通滤波”效应)。这会导致一个比特跳变后的连续相同比特在接收端看起来“更长”,这种现象称为码间干扰(ISI – Inter-Symbol Interference)。De-emphasis通过预衰减低频分量(连续比特)来补偿通道的高频损耗,使得在接收端,跳变比特和连续比特的眼图张开度更加一致,从而提高信号完整性。

54. 什么是接收器(RX)的均衡?为什么需要它? 答:

定义:均衡。是接收端采用的一种技术,用于补偿信号在传输通道中损失的高频分量,重塑被扭曲的信号。原因:与De-emphasis相同,都是为了对抗通道损耗引起的ISI。在更高速率(如Gen3及以上)下,仅靠TX De-emphasis不足以完全补偿损耗,必须在RX端也加入更强大的均衡器。RX均衡是链路训练和均衡过程的核心部分。

55. 解释CTLE和DFE的工作原理。 答:

CTLE (Continuous Time Linear Equalizer – 连续时间线性均衡器):

原理:一个模拟滤波器,其频率响应与通道的损耗特性相反。它在高频部分提供一个“峰值”(增益),而在低频部分提供较小的增益或衰减,从而提升被衰减的高频分量。特点:线性、无源(通常),无法完全消除ISI,但能显著改善信号。

DFE (Decision Feedback Equalizer – 判决反馈均衡器):

原理:一个非线性均衡器。它包含两个部分:1) 一个前向滤波器(如CTLE)进行初步均衡。2) 一个反馈环路:它对已经判决完成的先前比特进行加权,然后将这个加权值从当前输入的信号中减去,以消除先前比特对当前比特造成的ISI。特点:非常有效,能很好地消除后光标(Post-cursor)ISI,但设计复杂,有错误传播风险。

56. 什么是PCIe的参考时钟?常见的频率有哪些(100MHz, 125MHz)? 答:

定义:一个提供给PCIe设备(RC和EP)的精准、低抖动的时钟源,用于驱动PHY内部的PLL,以产生链路工作所需的高频时钟。常见频率:

100 MHz:这是最常见的参考时钟频率,由PCIe基规范定义。125 MHz:某些早期或特殊设计可能使用。注意:链路两端的设备必须使用相同频率的参考时钟。

57. 什么是Common Clock架构?什么是Separate Refclk架构? 答: 这是两种参考时钟的分布架构。

Common Clock (CC) 架构:

定义:链路的上下游设备使用同一个物理时钟源(例如,都由主板上的一个晶振提供)。优点:两端时钟同源,频率几乎完全相同,只有很小的相位偏移。这使得接收端的弹性缓冲区(EB)更容易管理时钟容差(clock tolerance),对BER要求更宽松。

Separate Refclk Independent SSC (SRIS) 架构:

定义:链路的上下游设备使用各自独立的时钟源(两个不同的晶振)。挑战:两个独立的时钟源即使标称频率相同,也存在细微的频率差和独立的扩频时钟(SSC)调制,导致更大的时钟容差和更快的漂移速率。这对接收端弹性缓冲区的设计和BER提出了更高要求。优点:简化PCB布线,无需分布时钟线到所有设备。

58. 什么是扩频时钟(SSC)?其目的是什么? 答:

定义:扩频时钟。一种有意地、缓慢地调制参考时钟频率的技术(通常以30-33kHz的调制速率,在中心频率上下±0.5%的范围内变化)。目的:降低电磁干扰(EMI)。将时钟能量分散到一个更宽的频率范围内,从而显著降低峰值辐射能量,帮助系统通过EMI合规性测试。SSC是PCIe的强制要求。

59. 描述PCIe链路训练和均衡(Link Training & Equalization)的完整过程。 答: 这是一个复杂的过程,目的是协商链路宽度、频率、极性,并最关键的是优化发送器和接收器的均衡设置,以补偿通道损耗。其主要阶段如下:

Polling:物理层建立比特锁定(Bit Lock)和符号锁定(Symbol Lock),交换TS1/TS2序列,协商链路速率和宽度。Configuration:确认链路宽度,分配Lane编号,完成Lane-to-Lane的De-skew(去偏移)。Recovery:这是均衡(EQ)发生的主要阶段。双方通过交换包含均衡系数(Preset或Coefficients)的TS1/TS2序列,采用一套“请求-响应-更新”的算法,迭代地调整TX和RX的均衡设置,直到找到能让接收端眼图张开度最好的配置。L0:训练完成,进入正常工作状态。

60. 在链路训练中,什么是TS1和TS2有序集(Ordered Sets)? 答:

定义:训练序列1和2。它们是用于链路训练和控制的一种特殊物理层数据包(不是TLP或DLLP),具有固定的格式和内容。作用:

在训练初期用于建立物理层通信。传达设备能力和训练要求(如支持的链路速率、链路宽度)。在Recovery阶段,用于交换均衡参数(TX preset请求、RX preset提示等)。传达电源管理状态改变等命令。

61. 训练序列中的Symbols(如COM, STP, SDP, END, EDB)各代表什么? 答: 这些是控制字符(K字符),用于界定数据包的边界。

COM (Comma):用于在接收端实现符号对齐(Symbol Alignment)。在8b/10b编码中,COM具有独特的比特模式(

K28.5

62. 什么是均衡预设(Preset)或系数(Coefficients)?如何协商? 答:

Preset/Coefficients:一组预先定义或动态计算的数字值,用于配置发送端的去加重/均衡或接收端的均衡器(CTLE/DFE)的强度。协商过程(在Recovery阶段):

下游设备(通常)通过TS1序列向上游设备请求一个特定的TX Preset。上游设备应用该Preset,并开始发送TS1序列。下游设备根据接收到的信号质量(如眼宽、眼高),判断该Preset是否有效。下游设备可能会请求一个新的Preset(更好或更差),通过迭代找到最佳的TX设置。同时,下游设备也会调整自己的RX均衡器设置(CTLE增益、DFE系数),以最大化信号余量。这个过程会持续多轮,直到双方都找到最优的均衡配置。

63. 解释Loopback模式及其在测试中的应用。 答:

定义:环回模式。一种测试模式,强制一个设备将其发送出的数据直接环回到自己的接收端,或者让远端设备将其接收到的数据发回给源端。类型:

近端环回 (Local Loopback):数据在发送器之后、串行器之前被环回到接收路径。用于测试设备的内部逻辑和PCS。远端环回 (Remote Loopback):数据发送到链路上,远端设备将接收到的数据原样发回。用于测试整个通道的完整性,包括PCB走线、连接器等。

应用:主要用于芯片和系统级的制造测试、调试和诊断,可以隔离故障是在芯片内部还是在外部通道。

64. 什么是电气空闲(Electrical Idle)?如何进入和退出? 答:

定义:一种低功耗状态,此时发送器停止发送差分数据,并将其输出驱动到一个共同的直流电压(DC common mode voltage)。进入:由上层(数据链路层或事务层)通过发送电气空闲有序集(EIOS) 或其他命令触发。退出:通过发送退出电气空闲有序集(EIEOS) 或开始正常的训练序列来唤醒链路。退出过程需要经过一段时间的唤醒和训练。

65. 什么是SKP有序集?它的作用是什么? 答:

定义:Skip有序集。一种定期在数据流中插入的特殊控制序列。作用:

时钟容差补偿:由于参考时钟可能存在细微的频率差异,发送端和接收端的时钟速率会有微小差别。弹性缓冲区(EB)用于吸收这种差异。当EB快满或快空时,通过添加或删除一个SKP有序集来动态调整数据流的长度,防止缓冲区上溢或下溢。通道偏斜校准:在链路训练中,也用于跨多Lane的De-skew。

66. 物理层逻辑子块中的Elastic Buffer的作用是什么? 答:

时钟容差补偿:如上所述,是SKP有序集操作的执行者,用于补偿两端时钟的频率差异。通道去偏斜(De-skew):在链路训练(Configuration阶段),通过对齐各Lane上弹性缓冲区的读指针,来补偿不同Lane之间的传输延迟差异(PCB走线长度不等)。

67. 什么是Bit Lock和Symbol Lock? 答:

Bit Lock:接收端CDR电路的工作状态,表示它已经成功地从输入的串行数据流中恢复出了比特时钟,能够正确地在每个比特单元的中心对数据进行采样。Symbol Lock (或 Word Lock/Block Lock):在实现Bit Lock之后,接收端通过搜索COM控制字符(K28.5)来确定符号(10-bit或130-bit)的边界。只有实现了Symbol Lock,接收器才能正确地将比特流解析成有意义的符号和数据包。

68. 描述通道到通道的偏移(Channel-to-Channel Skew)以及如何补偿。 答:

定义:由于PCB走线长度不可能绝对相等,信号在不同Lane上的传输延迟会有差异,这种差异称为Skew。补偿:在链路训练的Configuration阶段完成。

发送端同时在所有激活的Lane上发送一个特定的对齐模式(通常在TS1/TS2中)。接收端测量各Lane上该模式到达的时间差。接收端通过调整各Lane上弹性缓冲区(Elastic Buffer)的读延迟,来对齐所有Lane上的数据。走得慢的Lane(长走线)少延迟一些,走得快的Lane(短走线)多延迟一些。补偿完成后,所有Lane的数据就可以被同时读取和处理。

69. 物理层如何检测到远端接收器存在(Receiver Detection)? 答: 在链路初始化的Detect状态,发送端会进行接收器检测:

发送端向通道施加一个小的直流检测电压。然后测量从通道返回的电流。如果远端连接了一个接收器(终端电阻正确连接),返回的电流会在一个预期的范围内。如果通道是开放的(没有接收器),返回的电流会很小。 通过这种方式,发送端可以判断远端是否有设备存在,从而决定是否继续进行链路训练。

70. 什么是AC Coupling?为什么需要它?电容 typically 放在哪一侧? 答:

定义:交流耦合。指在发送器和接收器之间串联一个电容器(通常为75-200nF)。原因:

电平移位:不同的PCIe设备可能有不同的共模电压水平。AC耦合电容阻断了直流分量,允许两端设备使用自己独立的直流偏置电压,避免了直流电流冲突。故障保护:防止一个设备的故障(如短路)影响到链路上的其他设备。

位置:电容通常放置在发送器一侧(靠近TX芯片的引脚)。这在规范中是强制的,以确保互操作性。

71. 解释Tx/Rx端接(Termination)的要求。 答:

目的:阻抗匹配,防止信号在传输线末端反射,保证信号完整性。TX端接:发送器输出阻抗需要与通道的特性阻抗(通常为85-100Ω差分)匹配。RX端接:接收器输入端需要集成端接电阻(通常为100Ω差分),以匹配通道阻抗。在高速设计中,这个端接通常是精确的片上电阻。

72. 描述发送器眼图(Transmitter Eye Diagram)的构成和意义。 答:

构成:使用高速示波器,将发送器发出的无数个比特位的波形叠加显示在一个或多个单位间隔(UI)的窗口内,形成的图形。意义:

眼图张开度:眼的高度代表噪声容限,眼的宽度代表时序容限(抖动)。张开度越大,表示信号质量越好,误码率(BER)越低。评估TX性能:眼图是评估发送器输出信号质量的黄金标准,用于合规性测试。PCIe规范定义了严格的眼图模板(Eye Mask),发送器的信号必须完全落在这个模板之外才算合格。

73. 什么是眼图掩模(Eye Mask)? 答:

定义:一个定义了禁止区域的几何图形,覆盖在眼图之上。作用:用于合规性测试。如果发送器输出的信号波形有任何部分进入了眼图掩模的禁止区域,则该发送器 fails 测试。它提供了一个客观、可重复的Pass/Fail标准。

74. 解释插入损耗(Insertion Loss)、回波损耗(Return Loss)和串扰(Crosstalk)对信号完整性的影响。 答:

插入损耗:信号在通道中传输所产生的能量损耗(单位:dB)。它随频率升高而增加,是导致信号衰减和ISI的最主要因素。回波损耗:由于阻抗不连续(如连接器、过孔、线宽变化),部分信号能量被反射回源端。回波损耗越大,反射越严重,会干扰原始信号。串扰:相邻信号线之间的有害耦合。分为近端串扰(NEXT)和远端串扰(FEXT)。它会向受害网络注入噪声,降低信号的信噪比(SNR)。

75. 列出物理层中常见的抖动(Jitter)类型:RJ, DJ, ISI, DCD, PJ。 答:

TJ (Total Jitter):总抖动,在特定BER(通常1e-12)下测量。RJ (Random Jitter):随机抖动,由热噪声等随机因素引起,高斯分布,理论上无界。DJ (Deterministic Jitter):确定性抖动,由可识别的因素引起,有界。

DCD (Duty Cycle Distortion):占空比失真抖动,由信号的上升沿和下降沿时序不对称引起。ISI (Inter-Symbol Interference):码间干扰抖动,由通道损耗引起。PJ (Periodic Jitter):周期性抖动,由周期性噪声源(如开关电源)引起。

76. 什么是Bathtub曲线?它说明了什么? 答:

定义:一种描述误码率(BER)随采样时间位置变化的曲线,因其形状像浴缸而得名。说明:

曲线中间(缸底):BER最低,是最佳的采样点。曲线两侧(缸壁):BER急剧上升。左侧上升主要由DJ引起,右侧上升主要由RJ引起。意义:Bathtub曲线直观地展示了眼图在时间轴上的闭合情况和系统的时序容限,用于评估链路的抖动性能和确定最佳采样点。

77. 描述PCIe物理层的电源噪声抑制(PSNR)技术。 答: PSNR不是一项单一技术,而是一系列设计实践:

片上:使用低压差线性稳压器(LDO) 为敏感的模拟电路(如PLL, CDR)供电,以隔离数字电源噪声。板级:使用高质量的去耦电容(不同容值组合)为PCIe设备的电源引脚提供低阻抗的本地能量存储,滤除高频噪声。布线:电源平面要足够完整,提供低阻抗的返回路径。

78. 什么是PLL?在PCIe PHY中,Tx PLL和Rx CDR的作用是什么? 答:

PLL (Phase-Locked Loop – 锁相环):

作用:频率合成。它将输入的参考时钟倍频,产生PHY内部工作所需的高频比特时钟。Tx PLL:产生发送端串行器所需的精确高速时钟。

CDR (Clock Data Recovery – 时钟数据恢复电路):

作用:从接收到的串行数据流中提取出时钟信号。它没有独立的时钟输入,而是通过调整一个本地时钟源的相位和频率,使其与输入数据的跳变沿对齐,从而恢复出采样时钟和数据。它是接收端最关键的模块之一。

79. 物理层如何报告错误(如Receiver Error)? 答: 物理层错误(如8b/10b编码错误、弹性缓冲区上/下溢)通常会被计数,并通过状态寄存器(通常在PCIe Capability Structure中的Link Status寄存器)向上层报告。严重的物理层错误可能会触发链路重训练(进入Recovery状态)或更高级的错误处理机制。

80. 什么是Link Number和Lane Number?它们在训练中如何确定? 答:

Link Number:一个分配给端口的逻辑编号,用于在多端口设备(如Switch)中区分不同的链路。在训练中通过TS1/TS2交换确定。Lane Number:一个分配给每条Lane的逻辑编号(如Lane 0, Lane 1…)。在训练的Polling和Configuration阶段,双方通过交换TS1/TS2序列来协商和确认最终的Lane编号映射,解决可能的Lane Reversal。

81. 描述从Detect状态到L0状态的链路状态机跃迁过程。 答: 参考LTSSM (Link Training and Status State Machine):

Detect.Quiet:链路处于静止低功耗状态。Detect.Active:进行Receiver Detection,检测远端是否有设备。Polling:若检测到设备,则进入Polling状态,建立比特锁定和符号锁定,交换TS1/TS2,协商速率和宽度。Configuration:确认链路宽度,分配Lane编号,完成De-skew。Recovery:进行均衡训练,更新链路参数。L0:训练成功完成,进入正常工作状态,开始传输TLP/DLLP。

82. 什么是Disable状态?何时进入? 答:

定义:一种链路非活动状态,通常是由于不可恢复的错误或软件禁用命令导致。进入条件:

链路训练多次失败。收到软件发出的禁用命令。发生严重错误。

从Disable状态恢复通常需要** fundamental reset**。

83. 什么是Hot Reset?它与Fundamental Reset有何不同? 答:

Hot Reset:一种由软件或协议触发的、非破坏性的重置。它通过发送TS1序列(其中Hot Reset bit被置位)来发起,仅重置链路的逻辑状态和配置寄存器,而不会切断电源。用于从错误中恢复。Fundamental Reset:一种由硬件触发的、彻底的重置(如冷启动、按下复位按钮)。它会切断主电源再重新上电,或者断言PERST#信号,导致设备完全重启,所有状态丢失。

84. 什么是Beacon信号?用于什么场景? 答:

定义:一种由处于低功耗状态(如L2/L3)的设备发出的低频周期性信号。应用场景:主要用于唤醒和热插拔。

唤醒:设备在辅助电源(Vaux)下,可以通过发出Beacon信号来请求系统恢复主电源,从而唤醒整个链路。热插拔:在手动热插拔过程中,Attention Button被按下后,插槽会发出Beacon信号来通知系统。

85. 描述PCIe物理层的环回测试(Loopback Testing)方法。 答:

通过配置寄存器将链路置于Loopback模式(远端或近端)。测试设备发送特定的测试模式(PRBS – Pseudo-Random Bit Sequence 是最常用的)。在环回点,数据被返回。接收端将接收到的数据与发送的数据进行比较,计算误码率(BER)。如果BER低于阈值,则测试通过。这种方法可以精确隔离故障范围。

86. 用于PCIe物理层测试的常用仪器和方法有哪些? 答:

高速示波器:用于眼图、抖动、电压等模拟参数的测试。矢量网络分析仪(VNA):用于测量通道的S参数(插入损耗、回波损耗等)。BERT (Bit Error Rate Tester):用于误码率测试,发送PRBS码型并检测错误。协议分析仪:用于逻辑和协议层的调试,捕获和分析TLP/DLLP。误码注入:用于测试系统的容错和错误恢复能力。

87. 什么是S参数(S-Parameters)?它在通道分析中的作用是什么? 答:

定义:散射参数。一组描述一个线性电气网络如何在不同端口散射入射信号的复数参数。在PCIe中的作用:对通道进行建模和仿真。例如:

S21:插入损耗,直接反映通道的衰减特性。S11:输入回波损耗,反映发送端的阻抗匹配情况。S22:输出回波损耗,反映接收端的阻抗匹配情况。 通过S参数,可以在PCB制造前通过仿真软件(如ADS, HFSS)精确预测通道的性能,从而指导设计。

88. 解释TDR(时域反射计)在故障定位中的应用。 答:

原理:TDR向传输线发送一个快速上升沿的阶跃信号,并测量反射回来的信号。阻抗不连续点会导致信号反射。应用:通过分析反射信号的时间和幅度,可以:

定位阻抗不连续点的位置(如过孔、连接器、断路、短路)。测量不连续点的阻抗值。是诊断PCB布线故障(如线宽变化、stub)的强力工具。

89. 物理层如何支持多种数据速率(Gen1/2/3/4/5/6)的协商和切换? 答: 在链路训练的Polling阶段,双方设备通过TS1/TS2序列交换各自支持的最高速率。然后它们会从双方都支持的最高共同速率开始尝试建立链接。如果在该速率下训练失败(例如,由于通道质量差),链路会自动降速到下一个较低的共同速率再次尝试训练(例如,从Gen4降到Gen3)。这个过程可以是自动的,也可由软件控制。

90. 什么是Auto-Negotiation?它和Link Training是什么关系? 答:

Auto-Negotiation:通常指在以太网PHY中使用的、用于协商速率和双工模式的机制。在PCIe中:PCIe没有独立的Auto-Negotiation阶段。速率协商是Link Training过程的一个内在组成部分(主要在Polling阶段完成)。PCIe的LTSSM是一个更复杂、更集成的状态机,统一处理速率、宽度、均衡等所有物理层参数的协商。

91. 描述PCIe物理层中的低功耗状态(如L0s, L1, L2)及其退出延迟。 答:

L0s:快速休眠状态。仅接收器关闭,退出延迟极短(< 1 μs)。用于在极短的空闲时段省电。L1:深度休眠状态。收发器都关闭,退出延迟较长(几μs 到 几十μs)。用于较长的空闲时段,节省更多功耗。L2/L3 Ready:电源关闭的过渡状态。L3:链路关闭,主电源移除,仅留辅助电源。退出延迟非常长(毫秒级),需要完全重新训练。

92. 什么是PHY的电源门控(Power Gating)? 答: 一种先进的低功耗技术,在设备进入深度睡眠状态(如L2/L3)时,完全切断PHY部分电路的电源供应(而不仅仅是时钟门控),以将泄漏功耗降至近乎为零。唤醒时需要重新上电和初始化,因此退出延迟更长。

93. 描述PCIe CEM连接器对物理信号的规范要求。 答: PCIe Card Electromechanical (CEM) 规范对连接器和插卡有严格定义:

引脚定义:明确规定了每个引脚的功能(电源、地、差分对、PERST#, CLKREQ#, WAKE#等)。机械尺寸:定义了x1, x4, x8, x16等不同尺寸连接器的精确物理尺寸。电气特性:规定了连接器本身的阻抗、插损、串扰等参数要求,以确保信号完整性。热插拔支持:定义了与热插拔相关的引脚(如PRSNT#)及其行为。

94. 什么是Retimer?它的作用是什么?与Redriver有何区别? 答:

Retimer:一个智能有源器件。它包含完整的PCIe PHY(CDR, 均衡器),能够完全恢复数据流(重新生成时钟和数据),再发送出去。它可以彻底消除输入的抖动和噪声。Redriver:一个模拟放大器。它只是简单地放大(或均衡)输入的信号,但同时也会放大输入信号中的抖动和噪声。区别:Retimer性能更优,能延长传输距离,但成本更高,延迟也稍大。Redriver简单便宜,但无法改善信号质量,只能补偿损耗。在Gen4/5及以上的高速系统中,Retimer几乎是必须的。

95. 为什么在Gen4/5及以后Retimer变得愈发重要? 答: 因为随着速率翻倍(Gen4: 16 GT/s, Gen5: 32 GT/s),通道的插入损耗呈指数级增加(损耗与频率的平方根成正比)。主板PCB材料(如FR4)的损耗已经无法支持信号传输到足够的距离。Retimer被插入到通道中间,作为一个“信号再生中继站”,可以打破通道损耗的限制,使得高速信号能够传输得更远。

96. 描述PCIe物理层针对CXL协议所做的扩展。 答: http://CXL.io协议建立在PCIe物理层和电气层之上,完全兼容PCIe。CXL.cache和CXL.mem协议运行在更上层。因此,物理层本身不需要改变即可支持CXL。CXL设备在训练时会通过PCIe Capability结构中的扩展字段来宣告其CXL能力,但底层的信号、编码、训练过程与标准PCIe完全相同。

97. 在Gen6中,PAM4编码带来了哪些新的物理层挑战? 答: PAM4 (Pulse Amplitude Modulation 4-level) 每个符号代表2个比特(00, 01, 10, 11),有4个电压电平。

挑战:

信噪比(SNR)要求极高:电平之间的间距变小,对噪声和干扰更加敏感。线性度要求高:发送器和接收器需要非常线性的响应来处理多个电平。均衡更复杂:需要更强大的均衡器来补偿通道损耗对多电平信号的影响。前向纠错(FEC)成为必需:由于原始BER更高,必须引入强大的FEC来将BER降低到可接受的水平。

98. Gen6的FEC(前向纠错)是如何工作的?它解决了什么问题? 答:

问题:PAM4编码的原始BER较高,无法满足系统要求(通常要求<1e-12)。工作原理:FEC在发送端为数据块添加冗余的纠错码。在接收端,利用这些冗余信息来检测和纠正传输过程中发生的比特错误。代价:引入了额外的延迟(编码和解码时间)和少量的带宽开销(用于传输冗余位)。

99. 什么是PCIe的Flit Mode?(Gen6引入) 答:

FLIT (Flow Control Unit):流量控制单元。在Gen6中,一种新的、固定大小的数据包格式(256字节)。变化:在Gen6的Flit Mode下,传统的基于信用的流量控制不再以字节为单位,而是以整个FLIT为单位。这简化了控制逻辑,提高了效率,并与FEC协同工作(FEC在FLIT边界上进行操作)。

100. 描述PCIe物理层在芯片设计中的实现方式。 答: 绝大多数公司不会从头设计PCIe PHY,而是通过以下方式:

使用第三方IP:从专业的IP供应商(如Synopsys, Cadence, Alphawave)购买经过硅验证的PCIe PHY IP核。集成:将PHY IP与自研的PCIe控制器IP(处理事务层和数据链路层)集成在一起。工艺适配:IP供应商会将其PHY IP移植到不同的半导体工艺节点(如台积电5nm, 7nm等)上。挑战:PHY设计是混合信号设计,涉及高速模拟电路(SerDes),设计难度极大,需要深厚的专业知识和经验。

相关文章