在特斯拉柏林超级工厂的智能焊接线上,当0.1毫米级焊缝误差被实时捕捉时,是FPGA的并行计算能力在支撑;当产线机械臂完成每秒300次姿态调整时,是单片机在精准执行控制指令。这两种诞生于不同技术路线的电子器件,正在工业4.0时代形成独特的协同效应。根据SEMI最新数据,2024年全球FPGA市场规模达112亿美元,单片机出货量突破438亿颗,两者构成的智能控制系统已渗透至85%的现代工业设备中。

一、架构革命:并行与串行的根本分野

FPGA(现场可编程门阵列)的本质是硬件重构平台,其核心由可编程逻辑单元(CLB)、输入输出模块(IOB)和互连资源构成。这种架构允许开发者通过硬件描述语言(HDL)在硅片上”绘制”数字电路,形成完全定制的并行处理通道。以Xilinx UltraScale+系列为例,其内部包含526万个逻辑单元,可同时运行2000条独立运算路径。相较之下,单片机(MCU)采用冯·诺依曼或哈佛架构,将CPU、存储器、外设集成于单一芯片,通过顺序执行指令实现功能,如STM32H7系列需经过取指、译码、执行三个阶段完成单个操作。

FPGA

这种架构差异直接决定了性能边界。在5G基带处理场景中,Intel Arria 10 FPGA可实现每秒1.2Tb的数据吞吐,而即便是主频550MHz的STM32H7单片机,其串行处理模式也难以突破100Mb/s的速率瓶颈。更关键的是,FPGA的硬件并行性带来确定性的实时响应,在自动驾驶系统的激光雷达信号处理中,其延迟可控制在50ns以内,而基于中断机制的MCU方案一般存在±2ms的时间抖动。

MCU

二、开发范式:硬件描述与软件编程的思维鸿沟

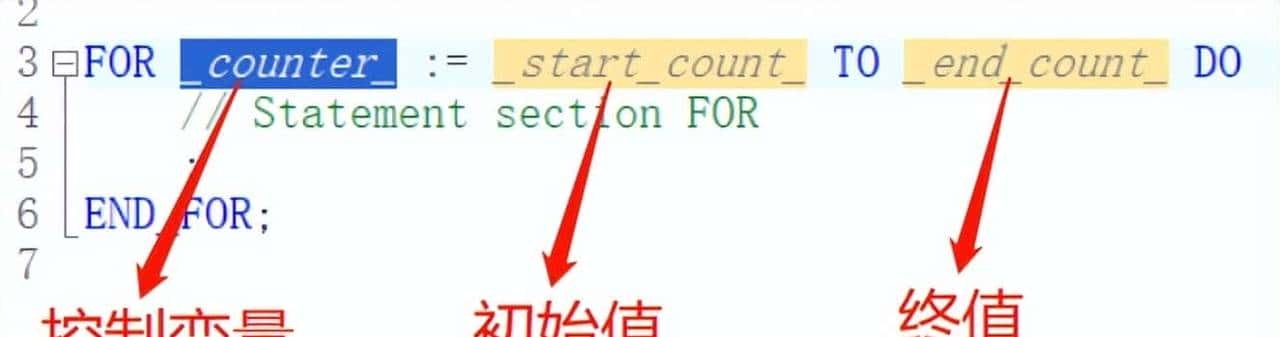

FPGA开发本质是硬件工程,开发者使用Verilog或VHDL语言描述电路结构。这种模式要求工程师具备数字电路设计能力,需准确规划时钟域、时序收敛、布线资源等物理约束。以Altera Cyclone V SoC为例,开发者需要手动配置156个引脚定义,并确保340MHz主频下建立时间余量大于0.3ns。反观单片机开发属于软件工程范畴,基于C/C++语言编写顺序执行的指令流,开发工具如Keil MDK可自动管理内存分配和外设驱动,显著降低技术门槛。

这种差异在算法实现层面尤为明显。当实现256点FFT变换时,STM32H7单片机需要2.1ms完成计算,而通过Vivado HLS工具在FPGA上生成的并行化硬件加速器,仅需0.8μs即可输出结果。但代价是开发周期:一个中等复杂度的FPGA项目一般需要3-6个月完成RTL设计、仿真验证和时序收敛,而同等功能的单片机程序开发周期可压缩至2周以内。

三、应用疆界:从控制中枢到加速引擎

在工业控制领域,单片机凭借低功耗、高可靠性稳居核心地位。三菱FX5U系列PLC控制器搭载RX72N单片机,可在-40℃至85℃环境下实现0.1ms级控制周期,支撑着全球68%的自动化产线。而FPGA则在高频交易系统大放异彩,Xilinx Virtex UltraScale+系列通过74.6万个DSP模块,将金融订单处理延迟压缩至740ns,较传统CPU方案提速1200倍。

新兴的AIoT领域凸显出融合趋势。地平线旭日X3芯片采用”ARM+FPGA”异构架构,其中Cortex-A53内核负责图像识别任务调度,而FPGA部分并行处理来自4路摄像头的1280×720@60fps视频流。这种分工使智能安防设备的功耗降低至5W,同时维持98%的人脸识别准确率。

四、功耗博弈:性能与能效的平衡艺术

在能量受限的嵌入式场景中,单片机展现出绝对优势。TI MSP430FR5994在休眠模式下功耗仅360nA,配合能量收集技术可实现十年免维护运行,广泛应用于智能水表等物联网终端。反观FPGA即便采用28nm工艺的Lattice ECP5系列,静态功耗仍高达300mW,动态功耗更随资源使用率线性增长,在移动设备中应用受限。

但高性能计算场景颠覆了这种认知。比特币矿机采用Xilinx VU9P FPGA构建计算集群,其每GH/s能效比达0.075J,较ASIC方案仅高18%,却具备可重构的灵活优势。这种特性使FPGA在航天领域备受青睐,NASA毅力号火星车的辐射加固型FPGA,可通过远程重构适应未知环境,功耗表现仍优于传统三重冗余MCU方案。

五、成本方程式:从芯片价格到系统价值的跃迁

单片机的成本优势体目前全生命周期。以STM32F103C8T6为例,其单价1.2美元即可满足多数控制需求,配合免费的STM32CubeMX工具链,开发成本可控制在500美元以内。而中端FPGA如Xilinx Artix-7 XC7A100T单价高达189美元,加上Vivado Design Edition软件授权费,单个项目前期投入常超2万美元。

但在系统级维度,FPGA的性价比优势逐渐显现。华为5G基站采用Intel Stratix 10 FPGA实现波束成形算法,单芯片替代原有DSP+MCU方案后,设备体积缩小60%,功耗降低45%,运维成本下降32%。更关键的是,FPGA支持硬件功能迭代,中兴通讯通过远程重构技术,使已部署的5G设备快速支持NR-U新频段,节省了数亿美元的硬件更换成本。

当智能驾驶域控制器开始集成可编程逻辑单元,当工业物联网终端嵌入神经网络加速器,FPGA与单片机的技术边界正在模糊。Xilinx Versal ACAP系列已实现ARM核与可编程逻辑的片上融合,其AI引擎的运算效能达到6.7TOPS/W,预示着异构计算的新纪元。这种演进揭示着电子技术的本质规律:没有永恒的替代关系,只有持续的技术融合。从1947年贝尔实验室的第一个晶体管,到如今支撑数字文明的数十亿智能设备,硬件与软件的协同进化,终将催生出超越人类想象的智能形态。

这才是真正的行家。技术表达力,文彩都很好。

作为自动化专业的老头,两种都学过

收藏了,感谢分享