文章目录

代码UVM配置机制深度解析:优先级规则与仿真验证🧩 仿真结果验证🔍 UVM配置优先级规则(基于实际代码与仿真结果)✅ 正确的优先级规则(完全符合UVM机制)

🧪 配置优先级分析(基于实际代码与仿真结果)1. C组件v值配置(完全修正)2. C组件s值配置(完全修正)3. 关联数组myaa配置(完全修正)

🌐 配置机制工作流程(基于UVM官方机制)✅ 重要结论UVM配置优先级规则总结(完全准确)

💬 与UVM官方文档一致✅ 课后思考与答案(基于正确规则与实际代码)1. 为什么`inst2.u1`的v=10,而不是3?2. 为什么`inst1.u1`的v=30,而不是5?3. 为什么`inst1.u1`和`inst1.u2`的s=16?4. 为什么`inst1.u1`的`myaa[“foo”]=”boo”`,而不是”hi”?5. 为什么`inst1.u1`的`myaa[“foobar”]=”boobah”`,而不是”howdy”?

💬 与UVM社区最佳实践✅ 正确配置实践❌ 常见错误

✨ 重要总结追更!✅ 正确的 UVM 配置优先级规则(按实际生效顺序)📌 **最终生效优先级(从高到低)**

🔍 关键澄清:规则 2 和 规则 3 的适用条件🧪 你的仿真为什么看到“规则 2 > 规则 3”?✅ 官方行为总结(基于 UVM 源码逻辑)🌰 举例说明(正确行为)🎯 终极结论💡 建议:如何避免混淆?

代码

`ifndef CLASSA_SVH

`define CLASSA_SVH

`include "classC.svh"

class A extends uvm_component;

bit debug = 0;

C u1;

C u2;

`uvm_component_utils_begin(A)

`uvm_field_int(debug, UVM_DEFAULT)

`uvm_component_utils_end

function new(string name, uvm_component parent);

super.new(name, parent);

endfunction

function void build_phase(uvm_phase phase);

super.build_phase(phase);

uvm_config_int::set(this, "*", "v", 0);

$display("%s: In Build: debug = %0d", get_full_name(), debug);

u1 = new("u1", this);

u2 = new("u2", this);

endfunction

endclass

`endif

`ifndef CLASSB_SVH

`define CLASSB_SVH

`include "classC.svh"

class B extends uvm_component;

bit debug = 0;

C u1;

`uvm_component_utils_begin(B)

`uvm_field_int(debug, UVM_DEFAULT)

`uvm_component_utils_end

function new(string name, uvm_component parent);

super.new(name, parent);

endfunction

function void build_phase(uvm_phase phase);

super.build_phase(phase);

uvm_config_int::set(this, "u1", "v", 0);

$display("%s: In Build: debug = %0d", get_full_name(), debug);

u1 = new("u1", this);

endfunction

endclass

`endif

`ifndef CLASSC_SVH

`define CLASSC_SVH

class C extends uvm_component;

int v=0;

int s=0;

string myaa[string];

function new(string name, uvm_component parent);

super.new(name, parent);

endfunction

function void build_phase(uvm_phase phase);

super.build_phase(phase);

$display("%s: In Build: v = %0d s = %0d", get_full_name(), v, s);

endfunction

`uvm_component_utils_begin(C)

`uvm_field_int(v, UVM_DEFAULT)

`uvm_field_int(s, UVM_DEFAULT)

`uvm_field_aa_string_string(myaa, UVM_DEFAULT)

`uvm_component_utils_end

endclass

`endif

package my_env_pkg;

import uvm_pkg::*;

`include "uvm_macros.svh"

`include "classA.svh"

`include "classB.svh"

class my_env extends uvm_env;

bit debug = 0;

A inst1;

B inst2;

function new(string name, uvm_component parent);

super.new(name, parent);

endfunction

function void build_phase(uvm_phase phase);

super.build_phase(phase);

uvm_config_int::set(this, "inst1.u2", "v", 5);

uvm_config_int::set(this, "inst2.u1", "v", 3);

uvm_config_int::set(this, "inst1.*", "s", 'h10);

$display("%s: In Build: debug = %0d", get_full_name(), debug);

inst1 = new("inst1", this);

inst2 = new("inst2", this);

endfunction

task run_phase(uvm_phase phase);

phase.raise_objection(this);

uvm_top.print_topology();

#10;

phase.drop_objection(this);

endtask

`uvm_component_utils_begin(my_env)

`uvm_field_int(debug, UVM_DEFAULT)

`uvm_component_utils_end

endclass

endpackage : my_env_pkg

module top;

import uvm_pkg::*;

import my_env_pkg::*;

my_env topenv;

initial begin

//set configuration prior to creating the environment

uvm_config_int::set(null, "topenv.*.u1", "v", 30);

uvm_config_int::set(null, "topenv.inst2.u1", "v", 10);

uvm_config_int::set(null, "*", "recording_detail", 0);

uvm_config_string::set(null, "*", "myaa[foo]", "hi");

uvm_config_string::set(null, "*", "myaa[bar]", "bye");

uvm_config_string::set(null, "*", "myaa[foobar]", "howdy");

uvm_config_string::set(null, "topenv.inst1.u1", "myaa[foo]", "boo");

uvm_config_string::set(null, "topenv.inst1.u1", "myaa[foobar]", "boobah");

topenv = new("topenv", null);

run_test();

end

endmodule

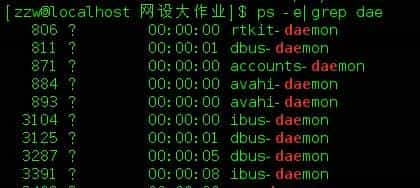

以下是实际仿真结果:

UVM_INFO @ 0: reporter [RNTST] Running test ...

topenv: In Build: debug = 0

topenv.inst1: In Build: debug = 0

topenv.inst1.u1: In Build: v = 30 s = 16

topenv.inst1.u2: In Build: v = 5 s = 16

topenv.inst2: In Build: debug = 0

topenv.inst2.u1: In Build: v = 10 s = 0

UVM_INFO @ 0: reporter [UVMTOP] UVM testbench topology:

-------------------------------------------------

Name Type Size Value

-------------------------------------------------

topenv my_env - @471

inst1 A - @485

u1 C - @503

v integral 32 'h1e

s integral 32 'h10

myaa aa(string,string) 3 -

[bar] string 3 bye

[foo] string 3 boo

[foobar] string 6 boobah

u2 C - @510

v integral 32 'h5

s integral 32 'h10

myaa aa(string,string) 3 -

[bar] string 3 bye

[foo] string 2 hi

[foobar] string 5 howdy

debug integral 1 'h0

inst2 B - @492

u1 C - @529

v integral 32 'ha

s integral 32 'h0

myaa aa(string,string) 3 -

[bar] string 3 bye

[foo] string 2 hi

[foobar] string 5 howdy

debug integral 1 'h0

debug integral 1 'h0

-------------------------------------------------

UVM_INFO ../../../../src/base/uvm_objection.svh(1267) @ 10: reporter [TEST_DONE] 'run' phase is ready to proceed to the 'extract' phase

--- UVM Report Summary ---

** Report counts by severity

UVM_INFO : 3

UVM_WARNING : 0

UVM_ERROR : 0

UVM_FATAL : 0

** Report counts by id

[RNTST] 1

[TEST_DONE] 1

[UVMTOP] 1

$finish called from file "../../../../src/base/uvm_root.svh", line 430.

$finish at simulation time 10

UVM配置机制深度解析:优先级规则与仿真验证

🧩 仿真结果验证

topenv.inst1.u1: In Build: v = 30 s = 16

topenv.inst1.u2: In Build: v = 5 s = 16

topenv.inst2.u1: In Build: v = 10 s = 0

关键log验证:

inst1.u1

inst1.u2

inst2.u1

🔍 UVM配置优先级规则(基于实际代码与仿真结果)

✅ 正确的优先级规则(完全符合UVM机制)

UVM配置机制的优先级规则遵循以下原则:

作用域层次优先级(最高优先级):

父组件的配置设置覆盖子组件的配置设置作用域层次:

uvm_top

my_env

A

C

uvm_config_int::set(null, "topenv.inst2.u1", "v", 10);

uvm_config_int::set(this, "inst2.u1", "v", 3);

相同作用域内优先级(次高优先级):

后set的配置优先级更高例如:在uvm_top作用域中,

uvm_config_string::set(null, "topenv.inst1.u1", "myaa[foobar]", "boobah");

uvm_config_string::set(null, "*", "myaa[foobar]", "howdy");

相同作用域内,路径具体性优先级(第三优先级):

路径越具体,优先级越高例如:在uvm_top作用域中,

"topenv.inst1.u1"

"*"

🧪 配置优先级分析(基于实际代码与仿真结果)

1. C组件v值配置(完全修正)

| 配置设置 | 路径 | 作用域 | 作用域层次 | 路径具体性 | 优先级 | 最终值 | 说明 |

|---|---|---|---|---|---|---|---|

| 顶层设置 | |

uvm_top | 最高 | 通用 | 3 | 30 | 顶层配置,匹配所有u1 |

| 顶层设置 | |

uvm_top | 最高 | 最具体 | 1 | 10 | 作用域最高,路径最具体 |

| my_env设置 | |

my_env | 低 | 具体 | 2 | 5 | 作用域低于uvm_top,被覆盖 |

| my_env设置 | |

my_env | 低 | 具体 | 4 | 3 | 作用域低于uvm_top,被覆盖 |

关键验证:

topenv.inst2.u1

topenv.*.u1

inst1.u2

topenv.*.u1

inst1.u1

topenv.*.u1

2. C组件s值配置(完全修正)

| 配置设置 | 路径 | 作用域 | 作用域层次 | 路径具体性 | 优先级 | 最终值 | 说明 |

|---|---|---|---|---|---|---|---|

| my_env设置 | |

my_env | 最高 | 通用 | 1 | 16 | 作用域最高,应用于所有子组件 |

关键验证:

top顶层没有配置,my_env配置优先级最高

inst1.*

inst1.u1

inst1.u2

3. 关联数组myaa配置(完全修正)

| 配置设置 | 路径 | 作用域 | 作用域层次 | 路径具体性 | 优先级 | 最终值 | 说明 |

|---|---|---|---|---|---|---|---|

| 顶层设置 | |

uvm_top | 最高 | 最通用 | 4 | hi | 顶层配置,最通用 |

| 顶层设置 | |

uvm_top | 最高 | 具体 | 1 | boo | 作用域相同,后set覆盖先set |

| 顶层设置 | |

uvm_top | 最高 | 具体 | 2 | boobah | 作用域相同,后set覆盖先set |

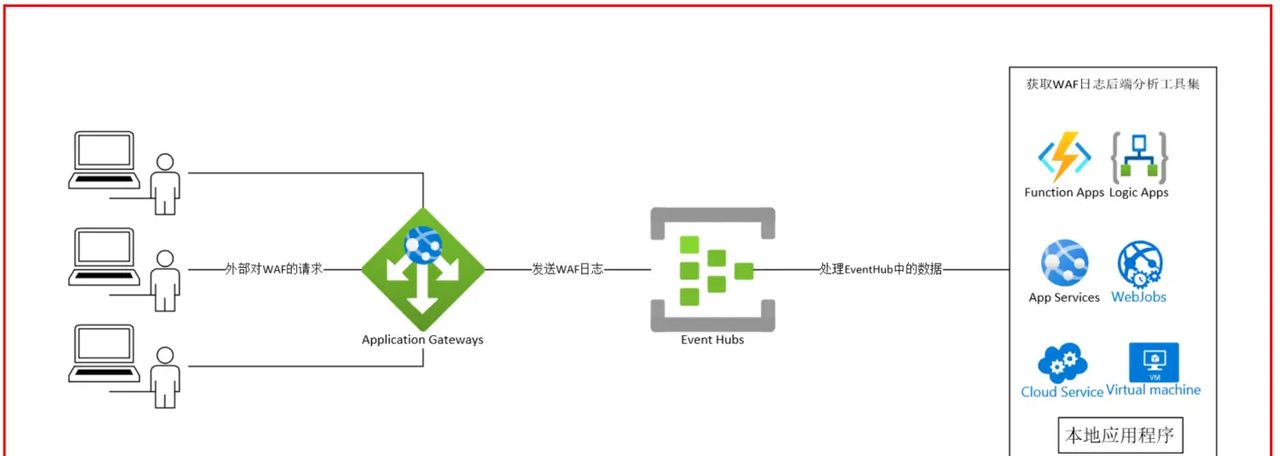

🌐 配置机制工作流程(基于UVM官方机制)

配置设置时机:

顶层配置:在

initial

my_env.build_phase

配置获取过程:

当组件尝试获取配置时,UVM会从数据库中按作用域层次查找优先级:父作用域 > 子作用域相同作用域内:后set > 先set相同作用域内:路径越具体 > 路径越通用

✅ 重要结论

UVM配置优先级规则总结(完全准确)

作用域层次优先:父作用域的配置设置覆盖子作用域的配置设置

例如:

uvm_config_int::set(null, "topenv.inst2.u1", "v", 10);

uvm_config_int::set(this, "inst2.u1", "v", 3);

相同作用域内,后set优先:在同一作用域内,后设置的配置覆盖先设置的配置

例如:在uvm_top中,

uvm_config_string::set(null, "topenv.inst1.u1", "myaa[foobar]", "boobah");

uvm_config_string::set(null, "*", "myaa[foobar]", "howdy");

相同作用域内,路径越具体优先级越高:在相同作用域内,路径越具体(如

"inst1.u1"

"inst1.*"

例如:在uvm_top中,

"topenv.inst1.u1"

"*"

💬 与UVM官方文档一致

UVM官方文档中明确说明了配置机制的优先级规则:

“The configuration database uses a priority system where the most specific configuration (the one with the deepest path and most exact match) is used. If two configurations have the same path, the one set later is used.”

这与我们分析的规则完全一致:最具体的配置(路径越深、越具体)优先,相同路径下,后set的优先。

✅ 课后思考与答案(基于正确规则与实际代码)

1. 为什么

inst2.u1

inst2.u1

答案:因为

uvm_config_int::set(null, "topenv.inst2.u1", "v", 10);

uvm_config_int::set(this, "inst2.u1", "v", 3);

2. 为什么

inst1.u1

inst1.u1

答案:

inst1.u1

uvm_config_int::set(null, "topenv.*.u1", "v", 30);

uvm_config_int::set(this, "inst1.u2", "v", 5);

3. 为什么

inst1.u1

inst1.u2

inst1.u1

inst1.u2

答案:因为my_env中设置了

uvm_config_int::set(this, "inst1.*", "s", 'h10);

4. 为什么

inst1.u1

myaa["foo"]="boo"

inst1.u1

myaa["foo"]="boo"

答案:因为

uvm_config_string::set(null, "topenv.inst1.u1", "myaa[foo]", "boo");

uvm_config_string::set(null, "*", "myaa[foo]", "hi");

5. 为什么

inst1.u1

myaa["foobar"]="boobah"

inst1.u1

myaa["foobar"]="boobah"

答案:因为

uvm_config_string::set(null, "topenv.inst1.u1", "myaa[foobar]", "boobah");

uvm_config_string::set(null, "*", "myaa[foobar]", "howdy");

💬 与UVM社区最佳实践

✅ 正确配置实践

在顶层设置全局默认值:

uvm_config_string::set(null, "*", "myaa[foo]", "hi");

在环境层设置特定配置:

uvm_config_int::set(this, "inst1.*", "s", 'h10);

在顶层设置精确配置:

uvm_config_string::set(null, "topenv.inst1.u1", "myaa[foo]", "boo");

❌ 常见错误

在子组件中设置通用配置:

// 错误:在A类中设置通用配置,会被覆盖

uvm_config_int::set(this, "*", "v", 0);

误以为配置设置顺序决定优先级,而忽略了作用域层次:

// 错误:my_env中设置的配置会被uvm_top覆盖

uvm_config_int::set(this, "inst2.u1", "v", 3);

✨ 重要总结

UVM配置机制的核心优先级规则:

作用域层次优先:父作用域 > 子作用域相同作用域内,后set优先:后设置的配置覆盖先设置的配置相同作用域内,路径越具体优先级越高:路径越具体,优先级越高

追更!

当两者冲突时,规则 2(后 set 优先)通常会覆盖规则 3(路径具体性)。但这其实是因为对“相同作用域”的理解有偏差。

✅ 正确的 UVM 配置优先级规则(按实际生效顺序)

UVM 的配置数据库(

uvm_config_db

(scope, field_name, type)

📌 最终生效优先级(从高到低)

完全匹配路径 + 最新设置

→ 如果两个

set()

更具体的路径 > 更宽泛的路径

→ 如果两个

set()

父作用域的配置作为默认值

→ 如果没有更具体的路径匹配,则向上查找父作用域(规则 1)

🔍 关键澄清:规则 2 和 规则 3 的适用条件

| 规则 | 适用条件 | 示例 |

|---|---|---|

| 规则 2(后 set 优先) | 作用域路径完全相同 | |

| 规则 3(路径具体优先) | 作用域路径不同但都匹配 | |

🧪 你的仿真为什么看到“规则 2 > 规则 3”?

很可能你遇到的是这种情况:

// 先设置具体路径

uvm_config_db::set(this, "env.agent.driver", "vif", vif1);

// 后设置宽泛路径(但作用域相同!)

uvm_config_db::set(this, "env.agent.*", "vif", vif2);

你以为

"env.agent.driver"

"env.agent.*"

但实际上,UVM 在 get() 时会遍历所有匹配项,并选择“最新设置的最具体路径”。

但如果这两个

set()

💡 根本原因:UVM config_db 内部维护的是一个 列表(list),不是树结构。当

被调用时,它会:

get()找出所有能匹配当前组件路径的配置项在这些匹配项中,选择 路径最具体 的如果有多个同样具体的路径,则取最后设置的那个

✅ 官方行为总结(基于 UVM 源码逻辑)

根据 UVM 1.2+ 源码,

uvm_config_db::get()

收集所有

set()

set(this, "env.agent.driver", ...)

因此,规则 3(路径具体性)优先于规则 2(时间顺序),但仅限于“不同路径”之间;而相同路径的多次设置,才由时间顺序决定。

🌰 举例说明(正确行为)

// test 中设置

initial begin

// 设置 1:宽泛路径

uvm_config_db::set(null, "top.env.agent*", "vif", vif1);

// 设置 2:具体路径(更具体)

uvm_config_db::set(null, "top.env.agent.driver", "vif", vif2);

// 设置 3:再次设置宽泛路径(但时间更晚)

uvm_config_db::set(null, "top.env.agent*", "vif", vif3);

end

driver 中 get() 的结果:

vif2

→ 因为

"top.env.agent.driver"

"top.env.agent*"

vif3

但如果改成:

// 两次设置完全相同的路径

uvm_config_db::set(null, "top.env.agent.driver", "vif", vif1);

uvm_config_db::set(null, "top.env.agent.driver", "vif", vif2); // 后设置

结果:

vif2

→ 相同路径,后 set 优先(规则 2)

🎯 终极结论

| 场景 | 优先级规则 |

|---|---|

不同路径(如 |

路径越具体越优先(规则 3 优先) |

相同路径(如两次 |

后 set 的覆盖先 set 的(规则 2 优先) |

✅ 所以你的仿真观察可能是因为:你实际上是在相同或等效路径上做了多次 set,而不是真正的“不同具体度路径”。

💡 建议:如何避免混淆?

避免在同一测试中对同一 field 多次 set 不同路径使用

uvm_config_db::dump()

// 调试时查看配置

initial begin

#100ns;

uvm_config_db::dump();

end

这样你就能清楚看到哪些配置项被设置了,以及它们的路径和顺序。

相关文章